–Φ–Α―¹–Ψ–≤–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η–Ι ―¹―É–Ω–Β―Ä–Κ–Ψ–Φ–Ω'―é―²–Β―Ä IBM Blue Gene /P–ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è βÄî ―Ü–Β ―³–Ψ―Ä–Φ–Α –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨, –≤ ―è–Κ–Η―Ö –Κ―•–Μ―¨–Κ–Α –¥―•–Ι –Ω―Ä–Ψ–≤–Ψ–¥―è―²―¨―¹―è –Ψ–¥–Ϋ–Ψ―΅–Α―¹–Ϋ–Ψ[ 1]

–³ –Κ―•–Μ―¨–Κ–Α ―Ä―•–Ζ–Ϋ–Η―Ö ―Ä―•–≤–Ϋ―•–≤ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨: –±―•―²–Ψ–≤–Η–Ι , ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι , –¥–Α–Ϋ–Η―Ö ―²–Α –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ –Ζ–Α–¥–Α―΅ . –ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è –Ζ–Α―¹―²–Ψ―¹–Ψ–≤―É―é―²―¨―¹―è –≤–Ε–Β –Ω―Ä–Ψ―²―è–≥–Ψ–Φ –±–Α–≥–Α―²―¨–Ψ―Ö ―Ä–Ψ–Κ―•–≤, –≤ –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Ψ–Φ―É –≤ –≤–Η―¹–Ψ–Κ–Ψ–Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è―Ö , –Α–Μ–Β –Ζ–Α―Ü―•–Κ–Α–≤–Μ–Β–Ϋ–Ϋ―è –Ϋ–Η–Φ –Ζ―Ä–Ψ―¹–Μ–Ψ ―²―•–Μ―¨–Κ–Η –Ϋ–Β–¥–Α–≤–Ϋ–Ψ, ―΅–Β―Ä–Β–Ζ ―³―•–Ζ–Η―΅–Ϋ―• –Ψ–±–Φ–Β–Ε–Β–Ϋ–Ϋ―è –Ζ―Ä–Ψ―¹―²–Α–Ϋ–Ϋ―è ―΅–Α―¹―²–Ψ―²–Η .[ 2] ―¹–Ω–Ψ–Ε–Η–≤–Α–Ϋ–Α –Ω–Ψ―²―É–Ε–Ϋ―•―¹―²―¨ (―• –≤―•–¥–Ω–Ψ–≤―•–¥–Ϋ–Ψ –≤–Η–¥―•–Μ–Β–Ϋ–Ϋ―è ―²–Β–Ω–Μ–Α) –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Α–Φ–Η ―¹―²–Α–Μ–Ψ –Ω―Ä–Ψ–±–Μ–Β–Φ–Ψ―é –≤ –Ψ―¹―²–Α–Ϋ–Ϋ―• ―Ä–Ψ–Κ–Η,[ 3] –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ―•–Ι –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä―• , –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Ψ–Φ―É –≤ ―³–Ψ―Ä–Φ―• –±–Α–≥–Α―²–Ψ―è–¥–Β―Ä–Ϋ–Η―Ö –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤ .[ 4]

–ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Η –Φ–Ψ–Ε―É―²―¨ –±―É―²–Η –≥―Ä―É–±–Ψ –Κ–Μ–Α―¹–Η―³―•–Κ–Ψ–≤–Α–Ϋ―• –Ζ–≥―•–¥–Ϋ–Ψ –Ζ ―Ä―•–≤–Ϋ–Β–Φ, –Ϋ–Α ―è–Κ–Ψ–Φ―É –Α–Ω–Α―Ä–Α―²–Ϋ–Β –Ζ–Α–±–Β–Ζ–Ω–Β―΅–Β–Ϋ–Ϋ―è –Ω―•–¥―²―Ä–Η–Φ―É―î –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ: –±–Α–≥–Α―²–Ψ―è–¥–Β―Ä–Ϋ―•―¹―²―¨ , –±–Α–≥–Α―²–Ψ–Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Ϋ―•―¹―²―¨ βÄî –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Η, ―â–Ψ –Φ–Α―é―²―¨ –±–Α–≥–Α―²–Ψ –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ–Η―Ö –Β–Μ–Β–Φ–Β–Ϋ―²―•–≤ –≤ –Φ–Β–Ε–Α―Ö –Ψ–¥–Ϋ–Ψ―½ –Φ–Α―à–Η–Ϋ–Η, –Α ―²–Α–Κ–Ψ–Ε –Κ–Μ–Α―¹―²–Β―Ä–Η , MPP , ―²–Α “ë―Ä―•–¥ βÄî ―¹–Η―¹―²–Β–Φ–Η ―â–Ψ –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―²―¨ –±–Α–≥–Α―²–Ψ –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤ –¥–Μ―è ―Ä–Ψ–±–Ψ―²–Η –Ϋ–Α–¥ –Ψ–¥–Ϋ–Η–Φ –Ζ–Α–≤–¥–Α–Ϋ–Ϋ―è–Φ. –Γ–Ω–Β―Ü―•–Α–Μ―•–Ζ–Ψ–≤–Α–Ϋ―• –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä–Η ―•–Ϋ–Ψ–¥―• –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―²―¨―¹―è –Ω–Ψ―Ä―è–¥ –Ζ ―²―Ä–Α–¥–Η―Ü―•–Ι–Ϋ–Η–Φ–Η –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α–Φ–Η, –¥–Μ―è –Ω―Ä–Η―¹–Κ–Ψ―Ä–Β–Ϋ–Ϋ―è –Ψ―¹–Ψ–±–Μ–Η–≤–Η―Ö –Ζ–Α–¥–Α―΅.

–ü―Ä–Ψ–≥―Ä–Α–Φ–Η –¥–Μ―è –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤ –Ω–Η―¹–Α―²–Η –Ζ–Ϋ–Α―΅–Ϋ–Ψ ―¹–Κ–Μ–Α–¥–Ϋ―•―à–Β, –Ϋ―•–Ε –¥–Μ―è –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Η―Ö[ 5] –Ω–Ψ–Φ–Η–Μ–Ψ–Κ , ―¹–Β―Ä–Β–¥ ―è–Κ–Η―Ö –Ϋ–Α–Ι–Ω–Ψ―à–Η―Ä–Β–Ϋ―•―à–Ψ―é ―î ―¹―²–Α–Ϋ –≥–Ψ–Ϋ–Η―²–≤–Η . –ö–Ψ–Φ―É–Ϋ―•–Κ–Α―Ü―•―è, ―²–Α ―¹–Η–Ϋ―Ö―Ä–Ψ–Ϋ―•–Ζ–Α―Ü―•―è –Ω―Ä–Ψ―Ü–Β―¹―•–≤ –Ζ–Α–Ζ–≤–Η―΅–Α–Ι –Ψ–¥–Ϋ–Α –Ζ –Ϋ–Α–Ι–±―•–Μ―¨―à–Η―Ö –Ω–Β―Ä–Β―à–Κ–Ψ–¥ –¥–Μ―è –¥–Ψ―¹―è–≥–Ϋ–Β–Ϋ–Ϋ―è ―Ö–Ψ―Ä–Ψ―à–Ψ―½ –Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Ψ―¹―²―• –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Ω―Ä–Ψ–≥―Ä–Α–Φ.

–€–Α–Κ―¹–Η–Φ–Α–Μ―¨–Ϋ–Η–Ι –Φ–Ψ–Ε–Μ–Η–≤–Η–Ι –Ω―Ä–Η―Ä―•―¹―² –Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Ψ―¹―²―• –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ―½ –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –≤–Η–Ζ–Ϋ–Α―΅–Α―î―²―¨―¹―è –Ζ–Α–Κ–Ψ–Ϋ–Ψ–Φ –ê–Φ–¥–Α–Μ–Α .

–ö–Ψ–Μ–Η―¹―¨ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Β –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è –±―É–Μ–Ψ ―¹–Ω―Ä–Α–≤–Ψ―é ―²―•–Μ―¨–Κ–Η ―²–Η―Ö –Ψ–¥–Η–Ϋ–Α–Κ―•–≤, ―è–Κ–Η―Ö ―Ü―•–Κ–Α–≤–Η–Μ–Η –Ζ–Α–≤–¥–Α–Ϋ–Ϋ―è –¥–Μ―è –≤–Β–Μ–Η–Κ–Η―Ö ―¹―É–Ω–Β―Ä–Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤ . –ê–Μ–Β ―²–Β–Ω–Β―Ä, –Κ–Ψ–Μ–Η –Ζ–≤–Η―΅–Α–Ι–Ϋ―• –¥–Ψ–¥–Α―²–Κ–Η –Ω–Ψ―΅–Α–Μ–Η –Ω―Ä–Α―Ü―é–≤–Α―²–Η –Ϋ–Α –±–Α–≥–Α―²–Ψ―è–¥–Β―Ä–Ϋ–Η―Ö –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α―Ö , –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Β –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è ―à–≤–Η–¥–Κ–Ψ ―¹―²–Α―î ―²–Β―Ö–Ϋ–Ψ–Μ–Ψ–≥―•―î―é, ―è–Κ―É –Ω–Ψ–≤–Η–Ϋ–Β–Ϋ –Ψ―¹–≤–Ψ―½―²–Η ―• –≤–Φ―•―²–Η –Ζ–Α―¹―²–Ψ―¹–Ψ–≤―É–≤–Α―²–Η –±―É–¥―¨-―è–Κ–Η–Ι –Ω―Ä–Ψ―³–Β―¹―•–Ι–Ϋ–Η–Ι ―Ä–Ψ–Ζ―Ä–Ψ–±–Ϋ–Η–Κ –ü–½. –ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Β –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è –Φ–Ψ–Ε–Β –±―É―²–Η ―¹–Κ–Μ–Α–¥–Ϋ–Η–Φ, –Α–Μ–Β –Ι–Ψ–≥–Ψ –Μ–Β–≥―à–Β –Ζ―Ä–Ψ–Ζ―É–Φ―•―²–Η, ―è–Κ―â–Ψ ―Ä–Α―Ö―É–≤–Α―²–Η –Ϋ–Β ¬Ϊ–≤–Α–Ε–Κ–Η–Φ¬Μ, –Α –Ω―Ä–Ψ―¹―²–Ψ ¬Ϊ―²―Ä–Ψ―Ö–Η ―•–Ϋ―à–Η–Φ¬Μ.

–Δ―Ä–Α–¥–Η―Ü―•–Ι–Ϋ–Ψ, –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –Ω–Η―à―É―²―¨―¹―è –¥–Μ―è –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨. –î–Μ―è ―Ä–Ψ–Ζ–≤'―è–Ζ–Κ―É –Ζ–Α–¥–Α―΅―• –Ω―Ä–Η–¥―É–Φ―É―é―²―¨ –Α–Μ–≥–Ψ―Ä–Η―²–Φ , ―è–Κ–Η–Ι ―Ä–Β–Α–Μ―•–Ζ–Ψ–≤―É―î―²―¨―¹―è –≤ –≤–Η–≥–Μ―è–¥―• –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Ψ―¹―²―• ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι. –Π―• ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―½ –≤–Η–Κ–Ψ–Ϋ―É―é―²―¨―¹―è –Ψ–¥–Ϋ–Η–Φ –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Ψ–Φ –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Α. –Θ –Κ–Ψ–Ε–Β–Ϋ –Φ–Ψ–Φ–Β–Ϋ―² ―΅–Α―¹―É –Φ–Ψ–Ε–Β –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η―¹―¨ ―²―•–Μ―¨–Κ–Η –Ψ–¥–Ϋ–Α ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―è, –Ω―•―¹–Μ―è –Ζ–Α–≤–Β―Ä―à–Β–Ϋ–Ϋ―è ―½―½ –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –Ω–Ψ―΅–Η–Ϋ–Α―î―²―¨―¹―è –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –Ϋ–Α―¹―²―É–Ω–Ϋ–Ψ―½.[ 6]

–½ ―•–Ϋ―à–Ψ–≥–Ψ –±–Ψ–Κ―É, –≤ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ–Φ―É –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―• –Ψ–¥–Ϋ–Ψ―΅–Α―¹–Ϋ–Ψ –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―²―¨ –Κ―•–Μ―¨–Κ–Α –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ–Η―Ö –Β–Μ–Β–Φ–Β–Ϋ―²―•–≤ –¥–Μ―è ―Ä–Ψ–Ζ–≤'―è–Ζ–Α–Ϋ–Ϋ―è –Ψ–¥–Ϋ―•―î―½ –Ζ–Α–¥–Α―΅―•. –Π–Β ―É–Φ–Ψ–Ε–Μ–Η–≤–Μ―é―î―²―¨―¹―è ―Ä–Ψ–Ζ–±–Η―²―²―è–Φ –Ζ–Α–¥–Α―΅―• –Ϋ–Α –Ω―•–¥–Ζ–Α–¥–Α―΅―•, –Κ–Ψ–Ε–Ϋ–Α –Ζ ―è–Κ–Η―Ö –Φ–Ψ–Ε–Β –±―É―²–Η –≤–Η―Ä―•―à–Β–Ϋ–Α –Ϋ–Β–Ζ–Α–Μ–Β–Ε–Ϋ–Ψ. –ü―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Ϋ―• –Β–Μ–Β–Φ–Β–Ϋ―²–Η –±―É–≤–Α―é―²―¨ ―Ä―•–Ζ–Ϋ–Η–Φ–Η ―²–Α –≤–Κ–Μ―é―΅–Α―é―²―¨ ―Ä―•–Ζ–Ϋ―• ―Ä–Β―¹―É―Ä―¹–Η, ―è–Κ –Ϋ–Α–Ω―Ä–Η–Κ–Μ–Α–¥ –Ψ–¥–Η–Ϋ –Κ–Ψ–Φ–Ω'―é―²–Β―Ä –Ζ –±–Α–≥–Α―²―¨–Φ–Α –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α–Φ–Η, –Κ―•–Μ―¨–Κ–Α –Ζ'―î–¥–Ϋ–Α–Ϋ–Η―Ö ―É –Φ–Β―Ä–Β–Ε―É –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤, ―¹–Ω–Β―Ü―•–Α–Μ―•–Ζ–Ψ–≤–Α–Ϋ–Β –Α–Ω–Α―Ä–Α―²–Ϋ–Β –Ζ–Α–±–Β–Ζ–Ω–Β―΅–Β–Ϋ–Ϋ―è, ―΅–Η –±―É–¥―¨-―è–Κ―É –Κ–Ψ–Φ–±―•–Ϋ–Α―Ü―•―é –Ω–Β―Ä–Β―Ä–Α―Ö–Ψ–≤–Α–Ϋ–Ψ–≥–Ψ –≤–Η―â–Β.[ 6]

–ü―Ä–Η―Ä―•―¹―² ―΅–Α―¹―²–Ψ―²–Η –±―É–≤ –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Η–Φ ―΅–Η–Ϋ–Ϋ–Η–Κ–Ψ–Φ –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Ψ―¹―²―• –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤ –Ζ ―¹–Β―Ä–Β–¥–Η–Ϋ–Η 1980-―²–Η―Ö –¥–Ψ 2004. –ß–Α―¹ ―Ä–Ψ–±–Ψ―²–Η –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –¥–Ψ―Ä―•–≤–Ϋ―é―î ―΅–Η―¹–Μ―É ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι, –Ω–Ψ–Φ–Ϋ–Ψ–Ε–Β–Ϋ–Ψ–Φ―É –Ϋ–Α ―¹–Β―Ä–Β–¥–Ϋ―•–Ι ―΅–Α―¹ –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―½. –Δ–Ψ–Φ―É –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è ―΅–Α―¹―²–Ψ―²–Η –Ζ–Φ–Β–Ϋ―à―É―î ―΅–Α―¹ –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –≤―¹―•―Ö –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Ϋ–Ψ-–Ζ–Α–Μ–Β–Ε–Ϋ–Η―Ö (–Κ–Ψ–Μ–Η –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Η–Φ ―Ä–Β―¹―É―Ä―¹–Ψ–Φ –≤–Η―¹―²―É–Ω–Α―î ―΅–Α―¹ –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α) –Ω―Ä–Ψ–≥―Ä–Α–Φ.[ 7]

–Δ–Η–Φ –Ϋ–Β –Φ–Β–Ϋ―à, ―¹–Ω–Ψ–Ε–Η–≤–Α–Ϋ–Α –Ω–Ψ―²―É–Ε–Ϋ―•―¹―²―¨ ―΅–Η–Ω―É –Ζ–Α–¥–Α―î―²―¨―¹―è ―Ä―•–≤–Ϋ―è–Ϋ–Ϋ―è–Φ P = C Ο½ V 2 Ο½ F P –Ω–Ψ―²―É–Ε–Ϋ―•―¹―²―¨ , V –Ϋ–Α–Ω―Ä―É–≥–Α –Ε–Η–≤–Μ–Β–Ϋ–Ϋ―è, C ―î–Φ–Ϋ―•―¹―²―¨ , ―â–Ψ –Ω–Β―Ä–Β–Ζ–Α―Ä―è–¥–Ε–Α―î―²―¨―¹―è –Ζ–Α –Ψ–¥–Η–Ϋ ―²–Α–Κ―² –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α (–Ω―Ä–Ψ–Ω–Ψ―Ä―Ü―•–Ι–Ϋ–Α ―΅–Η―¹–Μ―É ―²―Ä–Α–Ϋ–Ζ–Η―¹―²–Ψ―Ä―•–≤ , ―è–Κ―• –Ω–Β―Ä–Β–Φ–Η–Κ–Α―é―²―¨―¹―è ―É ―Ü―¨–Ψ–Φ―É ―²–Α–Κ―²―•), –Α F [ 8] Intel –≤―•–¥–Φ―•–Ϋ–Η–Μ–Ψ ―Ä–Ψ–Ζ―Ä–Ψ–±–Κ―É –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤ Tejas ―²–Α Jayhawk [en] [ 9]

–½–Α–Κ–Ψ–Ϋ –€―É―Ä–Α βÄî ―Ü–Β –Β–Φ–Ω―•―Ä–Η―΅–Ϋ–Β ―¹–Ω–Ψ―¹―²–Β―Ä–Β–Ε–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ ―²–Β, ―â–Ψ ―â―•–Μ―¨–Ϋ―•―¹―²―¨ ―²―Ä–Α–Ϋ–Ζ–Η―¹―²–Ψ―Ä―•–≤ –≤ –Φ―•–Κ―Ä–Ψ–Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α―Ö –Ω–Ψ–¥–≤–Ψ―é―î―²―¨―¹―è –Κ–Ψ–Ε–Ϋ–Η―Ö 18-24 –Φ―•―¹―è―Ü―•.[ 10]

–™―Ä–Α―³―•―΅–Ϋ–Β –Ζ–Ψ–±―Ä–Α–Ε–Β–Ϋ–Ϋ―è –Ζ–Α–Κ–Ψ–Ϋ―É –ê–Φ–¥–Α–Μ–Α . –ü―Ä–Η―¹–Κ–Ψ―Ä–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –Ω―Ä–Η ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é–≤–Α–Ϋ–Ϋ―• –Ζ–Α–Μ–Β–Ε–Η―²―¨ –≤―•–¥ ―²–Ψ–≥–Ψ ―è–Κ―É ―΅–Α―¹―²–Η–Ϋ―É –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –Φ–Ψ–Ε–Ϋ–Α –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ. –ù–Α–Ω―Ä–Η–Κ–Μ–Α–¥, ―è–Κ―â–Ψ 90 % –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –Φ–Ψ–Ε–Ϋ–Α –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ, ―²–Β–Ψ―Ä–Β―²–Η―΅–Ϋ–Η–Φ –Φ–Α–Κ―¹–Η–Φ―É–Φ–Ψ–Φ –Ω―Ä–Η―¹–Κ–Ψ―Ä–Β–Ϋ–Ϋ―è –Ω―Ä–Η –Ζ–Α–Ω―É―¹–Κ―É ―½―½ –Ϋ–Α –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―•–Ι –Φ–Α―à–Η–Ϋ―• –±―É–¥–Β –¥–Β―¹―è―²–Η–Κ―Ä–Α―²–Ϋ–Β, –Ϋ–Β–Ζ–Α–Μ–Β–Ε–Ϋ–Ψ –≤―•–¥ ―²–Ψ–≥–Ψ, ―¹–Κ―•–Μ―¨–Κ–Η –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤ –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―î―²―¨―¹―è. –û–Ω―²–Η–Φ–Α–Μ―¨–Ϋ–Η–Φ –Ω―Ä–Η―¹–Κ–Ψ―Ä–Β–Ϋ–Ϋ―è–Φ –≤―•–¥ ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é–≤–Α–Ϋ–Ϋ―è –Φ–Ψ–≥–Μ–Ψ –± –±―É―²–Η –Μ―•–Ϋ―•–Ι–Ϋ–Β βÄî –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è –Κ―•–Μ―¨–Κ–Ψ―¹―²―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤ –≤–¥–≤―•―΅―• –Φ–Α―î –≤–¥–≤―•―΅―• ―¹–Κ–Ψ―Ä–Ψ―΅―É–≤–Α―²–Η ―΅–Α―¹ –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è. –ù–Α―¹―²―É–Ω–Ϋ–Β –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è –Κ―•–Μ―¨–Κ–Ψ―¹―²―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤ –≤–¥–≤―•―΅―• –Φ–Α–Μ–Ψ –± –Ζ–Ϋ–Ψ–≤―É –Ω―Ä–Η―¹–Κ–Ψ―Ä―é–≤–Α―²–Η –Ω―Ä–Ψ–≥―Ä–Α–Φ―É. –Δ–Η–Φ –Ϋ–Β –Φ–Β–Ϋ―à, –Μ–Η―à –Κ―•–Μ―¨–Κ–Α –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Α–Μ–≥–Ψ―Ä–Η―²–Φ―•–≤ –¥–Ψ―¹―è–≥–Α―é―²―¨ ―²–Α–Κ–Ψ–≥–Ψ –Ω―Ä–Η―¹–Κ–Ψ―Ä–Β–Ϋ–Ϋ―è. –ë―•–Μ―¨―à―•―¹―²―¨ –Ζ –Ϋ–Η―Ö –Φ–Α―é―²―¨ –Φ–Α–Ι–Ε–Β –Μ―•–Ϋ―•–Ι–Ϋ–Β –Ω―Ä–Η―¹–Κ–Ψ―Ä–Β–Ϋ–Ϋ―è –Ω―Ä–Η –Ϋ–Β–≤–Β–Μ–Η–Κ―•–Ι –Κ―•–Μ―¨–Κ–Ψ―¹―²―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤, ―è–Κ–Β ―¹–Ω–Ψ–≤―•–Μ―¨–Ϋ―é―î―²―¨―¹―è –¥–Ψ –Κ–Ψ–Ϋ―¹―²–Α–Ϋ―²–Η –Ω―Ä–Η –≤–Β–Μ–Η–Κ―•–Ι –Κ―•–Μ―¨–Κ–Ψ―¹―²―• –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ–Η―Ö –Β–Μ–Β–Φ–Β–Ϋ―²―•–≤.

–ü–Ψ―²–Β–Ϋ―Ü―•–Ι–Ϋ–Β –Ω―Ä–Η―¹–Κ–Ψ―Ä–Β–Ϋ–Ϋ―è –Α–Μ–≥–Ψ―Ä–Η―²–Φ―É –Ω―Ä–Η –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―• ―΅–Η―¹–Μ–Α –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤ –Ζ–Α–¥–Α―î―²―¨―¹―è –Ζ–Α–Κ–Ψ–Ϋ–Ψ–Φ –ê–Φ–¥–Α–Μ–Α , ―â–Ψ –≤–Ω–Β―Ä―à–Β –±―É–≤ ―¹―³–Ψ―Ä–Φ―É–Μ―¨–Ψ–≤–Α–Ϋ–Η–Ι –î–Ε–Η–Ϋ–Ψ–Φ –ê–Φ–¥–Α–Μ–Β–Φ ―É 1960-―²–Η―Ö.[ 11]

S

=

1

1

− β࣠-->

P

{\displaystyle S={\frac {1}{1-P}}}

–î–Β

S

{\displaystyle S}

P

{\displaystyle P}

[ 12]

–½–Α–Κ–Ψ–Ϋ –™―É―¹―²–Α―³―¹–Ψ–Ϋ–Α ―Ü–Β ―•–Ϋ―à–Η–Ι –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ–Η–Ι –Ζ–Α–Κ–Ψ–Ϋ, ―â–Ψ ―¹–Η–Μ―¨–Ϋ–Ψ –Ω–Ψ–≤'―è–Ζ–Α–Ϋ–Η–Ι –Ζ –Ζ–Α–Κ–Ψ–Ϋ–Ψ–Φ –ê–Φ–¥–Α–Μ–Α. –ô–Ψ–≥–Ψ –Φ–Ψ–Ε–Ϋ–Α ―¹―³–Ψ―Ä–Φ―É–Μ―é–≤–Α―²–Η ―²–Α–Κ:

–ü―Ä–Η–Ω―É―¹―²–Η–Φ–Ψ ―â–Ψ –Ζ–Α–¥–Α―΅–Α –Φ–Α―î –¥–≤―• –Ϋ–Β–Ζ–Α–Μ–Β–Ε–Ϋ―• ―΅–Α―¹―²–Η–Ϋ–Η, A ―²–Α B. B –Ζ–Α–Ι–Φ–Α―î 25 % ―΅–Α―¹―É –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨. –î–Ψ–Κ–Μ–Α–≤―à–Η –Ω–Β–≤–Ϋ–Η―Ö –Ζ―É―¹–Η–Μ―¨ –Ω―Ä–Ψ–≥―Ä–Α–Φ―•―¹―² –Φ–Ψ–Ε–Β –Ζ―Ä–Ψ–±–Η―²–Η ―Ü―é ―΅–Α―¹―²–Η–Ϋ―É –≤ –Ω'―è―²―¨ ―Ä–Α–Ζ―•–≤ ―à–≤–Η–¥―à–Ψ―é, –Α–Μ–Β ―Ü–Β –Ϋ–Β–Ϋ–Α–±–Α–≥–Α―²–Ψ –Ζ–Φ–Β–Ϋ―à–Η―²―¨ ―΅–Α―¹ –≤―¹―¨–Ψ–≥–Ψ –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è. –Δ–Η–Φ –Ϋ–Β –Φ–Β–Ϋ―à, –Φ–Ψ–Ε–Μ–Η–≤–Ψ –¥–Μ―è ―²–Ψ–≥–Ψ ―â–Ψ–± –Ω―Ä–Η―¹–Κ–Ψ―Ä–Η―²–Η ―΅–Α―¹―²–Η–Ϋ―É A –≤–¥–≤―•―΅―• –Ω–Ψ―²―Ä―•–±–Ϋ–Ψ –Φ–Β–Ϋ―à–Β –Ζ―É―¹–Η–Μ―¨, –Α–Μ–Β ―Ü–Β –Ω―Ä–Η―¹–Κ–Ψ―Ä–Η―²―¨ –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –≤―¹―•―î―½ –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –Ϋ–Α–±–Α–≥–Α―²–Ψ ―¹–Η–Μ―¨–Ϋ―•―à–Β –Ϋ―•–Ε –Ψ–Ω―²–Η–Φ―•–Ζ–Α―Ü―•―è B, –Ω–Ψ–Ω―Ä–Η ―²–Β, ―â–Ψ B –Φ–Ψ–Ε–Ϋ–Α –Ψ–Ω―²–Η–Φ―•–Ζ―É–≤–Α―²–Η ―¹–Η–Μ―¨–Ϋ―•―à–Β.

S

(

P

)

=

P

− β࣠-->

α Έ± -->

(

P

− β࣠-->

1

)

{\displaystyle S(P)=P-\alpha (P-1)\,}

–¥–Β

P

{\displaystyle P}

S

{\displaystyle S}

α Έ± -->

{\displaystyle \alpha }

[ 13]

–†–Ψ–Ζ―É–Φ―•–Ϋ–Ϋ―è –Ζ–Α–Μ–Β–Ε–Ϋ–Ψ―¹―²–Β–Ι –¥–Α–Ϋ–Η―Ö –¥―É–Ε–Β –≤–Α–Ε–Μ–Η–≤–Β –¥–Μ―è ―Ä–Ψ–Ζ―Ä–Ψ–±–Κ–Η –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Α–Μ–≥–Ψ―Ä–Η―²–Φ―•–≤ . –•–Ψ–¥–Ϋ–Α –Ω―Ä–Ψ–≥―Ä–Α–Φ–Α –Ϋ–Β –Φ–Ψ–Ε–Β –Ω―Ä–Α―Ü―é–≤–Α―²–Η ―à–≤–Η–¥―à–Β –Ϋ―•–Ε –Ϋ–Α–Ι–¥–Ψ–≤―à–Η–Ι –Μ–Α–Ϋ―Ü―é–≥ –Ζ–Α–Μ–Β–Ε–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ (–≤―•–¥–Ψ–Φ–Η–Ι ―è–Κ –Κ―Ä–Η―²–Η―΅–Ϋ–Η–Ι ―à–Μ―è―Ö ), –±–Ψ –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è, ―â–Ψ –Ζ–Α–Μ–Β–Ε–Α―²―¨ –≤―•–¥ –Ω–Ψ–Ω–Β―Ä–Β–¥–Ϋ―•―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ –≤ –Μ–Α–Ϋ―Ü―é–≥―É –Φ–Α―é―²―¨ –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η―¹―¨ –Ψ–¥–Ϋ–Β –Ζ–Α –Ψ–¥–Ϋ–Η–Φ. –Δ–Η–Φ –Ϋ–Β –Φ–Β–Ϋ―à, –±―•–Μ―¨―à―•―¹―²―¨ –Α–Μ–≥–Ψ―Ä–Η―²–Φ―•–≤ –Ϋ–Β ―¹–Κ–Μ–Α–¥–Α―é―²―¨―¹―è –Μ–Η―à –Ζ –¥–Ψ–≤–≥–Ψ–≥–Ψ –Μ–Α–Ϋ―Ü―é–≥–Α –Ζ–Α–Μ–Β–Ε–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨; –Ζ–Α–Ζ–≤–Η―΅–Α–Ι ―î ―à–Α–Ϋ―¹–Η –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η –Ϋ–Β–Ζ–Α–Μ–Β–Ε–Ϋ―• –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ.

–Ξ–Α–Ι

P

i

{\displaystyle P_{i}}

P

j

{\displaystyle P_{j}}

[ 14]

P

i

{\displaystyle P_{i}}

I

i

{\displaystyle I_{i}}

O

i

{\displaystyle O_{i}}

P

j

{\displaystyle P_{j}}

P

i

{\displaystyle P_{i}}

P

j

{\displaystyle P_{j}}

I

j

∩ βà© -->

O

i

=

∅ βàÖ -->

,

{\displaystyle I_{j}\cap O_{i}=\varnothing ,\,}

I

i

∩ βà© -->

O

j

=

∅ βàÖ -->

,

{\displaystyle I_{i}\cap O_{j}=\varnothing ,\,}

O

i

∩ βà© -->

O

j

=

∅ βàÖ -->

.

{\displaystyle O_{i}\cap O_{j}=\varnothing .\,}

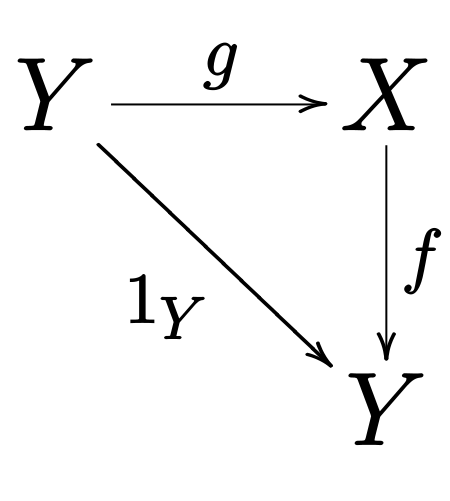

–ü–Ψ―Ä―É―à–Β–Ϋ–Ϋ―è –Ω–Β―Ä―à–Ψ―½ ―É–Φ–Ψ–≤–Η ―¹―²–≤–Ψ―Ä―é―î –Ζ–Α–Μ–Β–Ε–Ϋ―•―¹―²―¨ –Ω–Ψ―²–Ψ–Κ―É, ―Ä–Β–Ζ―É–Μ―¨―²–Α―² ―Ä–Ψ–±–Ψ―²–Η –Ω–Β―Ä―à–Ψ―½ ―΅–Α―¹―²–Η–Ϋ–Η –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―î―²―¨―¹―è –¥―Ä―É–≥–Ψ―é. –î―Ä―É–≥–Α ―É–Φ–Ψ–≤–Α –Ω―Ä–Β–¥―¹―²–Α–≤–Μ―è―î –Α–Ϋ―²–Η–Ζ–Α–Μ–Β–Ε–Ϋ―•―¹―²―¨, –Κ–Ψ–Μ–Η –¥―Ä―É–≥–Α ―΅–Α―¹―²–Η–Ϋ–Α –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –Ω–Β―Ä–Β–Ω–Η―¹―É―î –Ζ–Φ―•–Ϋ–Ϋ―É, ―â–Ψ –Ω–Ψ―²―Ä―•–±–Ϋ–Α –Ω–Β―Ä―à―•–Ι –Ω―Ä–Ψ–≥―Ä–Α–Φ―•. –Δ―Ä–Β―²―è, ―²–Α –Ψ―¹―²–Α–Ϋ–Ϋ―è ―É–Φ–Ψ–≤–Α –Ω―Ä–Β–¥―¹―²–Α–≤–Μ―è―î –Ζ–Α–Μ–Β–Ε–Ϋ―•―¹―²―¨ –≤–Η–≤–Ψ–¥―•–≤: –Κ–Ψ–Μ–Η –¥–≤―• ―΅–Α―¹―²–Η–Ϋ–Η –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –Ζ–Α–Ω–Η―¹―É―é―²―¨ –¥–Α–Ϋ―• –≤ –Ψ–¥–Ϋ―É –Ι ―²―É –Ε –Ζ–Φ―•–Ϋ–Ϋ―É, –Κ―•–Ϋ―Ü–Β–≤–Η–Ι ―Ä–Β–Ζ―É–Μ―¨―²–Α―² –Φ–Α―î –Ψ―²―Ä–Η–Φ―É–≤–Α―²–Η―¹―¨ –≤―•–¥ ―΅–Α―¹―²–Η–Ϋ–Η, ―â–Ψ –Μ–Ψ–≥―•―΅–Ϋ–Ψ –≤–Η–Κ–Ψ–Ϋ―É―î―²―¨―¹―è –Ψ―¹―²–Α–Ϋ–Ϋ―¨–Ψ―é.[ 15]

–î–Α–≤–Α–Ι―²–Β –Ω―Ä–Η–¥―É–Φ–Α―î–Φ–Ψ –¥–Β―è–Κ―• ―³―É–Ϋ–Κ―Ü―•―½, ―â–Ψ –¥–Β–Φ–Ψ–Ϋ―¹―²―Ä―É―é―²―¨ –Κ―•–Μ―¨–Κ–Α ―²–Η–Ω―•–≤ –Ζ–Α–Μ–Β–Ε–Ϋ–Ψ―¹―²–Β–Ι:

1: function Dep(a, b)

2: c := a¬Ζb

3: d := 2¬Ζc

–û–Ω–Β―Ä–Α―²–Ψ―Ä 3 –≤ Dep(a,b) –Ϋ–Β –Φ–Ψ–Ε–Β –±―É―²–Η –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Η–Φ –Ω–Β―Ä–Β–¥ (―΅–Η –Ϋ–Α–≤―•―²―¨ –Ψ–¥–Ϋ–Ψ―΅–Α―¹–Ϋ–Ψ –Ζ) –Ψ–Ω–Β―Ä–Α―²–Ψ―Ä–Ψ–Φ 2, –±–Ψ –Ψ–Ω–Β―Ä–Α―Ü―•―è 3 –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―î ―Ä–Β–Ζ―É–Μ―¨―²–Α―² ―Ä–Ψ–±–Ψ―²–Η –Ψ–Ω–Β―Ä–Α―Ü―•―½ 2. –£–Ψ–Ϋ–Α –Ω–Ψ―Ä―É―à―É―î ―É–Φ–Ψ–≤―É 1, ―²–Ψ–Φ―É –Φ–Α―î–Φ–Ψ –Ζ–Α–Μ–Β–Ε–Ϋ―•―¹―²―¨ –Ω–Ψ―²–Ψ–Κ―É.

1: function NoDep(a, b)

2: c := a¬Ζb

3: d := 2¬Ζb

4: e := a+b

–£ ―Ü―¨–Ψ–Φ―É –Ω―Ä–Η–Κ–Μ–Α–¥―• –Φ―•–Ε –Ψ–Ω–Β―Ä–Α―Ü―•―è–Φ–Η –Ϋ–Β–Φ–Α―î –Ζ–Α–Μ–Β–Ε–Ϋ–Ψ―¹―²–Β–Ι, ―²–Ψ–Φ―É –≤–Ψ–Ϋ–Η –Φ–Ψ–Ε―É―²―¨ –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η―¹―¨ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ.

–Θ–Φ–Ψ–≤–Η –ë–Β―Ä–Ϋ―à―²–Β–Ι–Ϋ–Α –Ϋ–Β –¥–Ψ–Ζ–≤–Ψ–Μ―è―é―²―¨ –¥―•–Μ–Η―²–Η –Ω–Α–Φ'―è―²―¨ –Φ―•–Ε ―Ä―•–Ζ–Ϋ–Η–Φ–Η –Ω―Ä–Ψ―Ü–Β―¹–Α–Φ–Η. –Δ–Ψ–Φ―É, –Ω–Ψ―²―Ä―•–±–Ϋ–Β –Ω―Ä–Η–Φ―É―¹–Ψ–≤–Β –≤–Ω–Ψ―Ä―è–¥–Κ―É–≤–Α–Ϋ–Ϋ―è –¥–Ψ―¹―²―É–Ω―É –¥–Ψ –¥–Α–Ϋ–Η―Ö, ―è–Κ ―¹–Β–Φ–Α―³–Ψ―Ä–Η , –±–Α―Ä'―î―Ä–Η , ―²–Α ―•–Ϋ―à―• –Φ–Β―²–Ψ–¥–Η ―¹–Η–Ϋ―Ö―Ä–Ψ–Ϋ―•–Ζ–Α―Ü―•―½ .

–ü―•–¥–Ζ–Α–¥–Α―΅―• –≤ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―•–Ι –Ω―Ä–Ψ–≥―Ä–Α–Φ―• ―΅–Α―¹―²–Ψ –Ϋ–Α–Ζ–Η–≤–Α―é―²―¨ –Ϋ–Η―²–Κ–Α–Φ–Η . –î–Β―è–Κ―• –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä–Η –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―²―¨ –Φ–Β–Ϋ―à―•, –Μ–Β–≥―à―• –≤–Β―Ä―¹―•―½ –Ϋ–Η―²–Ψ–Κ, ―â–Ψ –Ϋ–Α–Ζ–Η–≤–Α―é―²―¨―¹―è –≤–Ψ–Μ–Ψ–Κ–Ϋ–Α–Φ–Η , –≤ ―²–Ψ–Ι ―΅–Α―¹ ―è–Κ ―•–Ϋ―à―• –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―²―¨ –±―•–Μ―¨―à―• –≤–Β―Ä―¹―•―½, ―â–Ψ –Ϋ–Α–Ζ–Η–≤–Α―é―²―¨―¹―è –Ω―Ä–Ψ―Ü–Β―¹–Α–Φ–Η . –Δ–Η–Φ –Ϋ–Β –Φ–Β–Ϋ―à, ¬Ϊ–Ϋ–Η―²–Κ–Η¬Μ –Ζ–Α–Ζ–≤–Η―΅–Α–Ι –Ω―Ä–Η–Ι–Φ–Α―é―²―¨―¹―è ―è–Κ –Ζ–Α–≥–Α–Μ―¨–Ϋ–Η–Ι ―²–Β―Ä–Φ―•–Ϋ –¥–Μ―è –Ω―•–¥–Ζ–Α–¥–Α―΅. –ù–Η―²–Κ–Η ―΅–Α―¹―²–Ψ –Ω–Ψ―²―Ä–Β–±―É―é―²―¨ ―¹–Η–Ϋ―Ö―Ä–Ψ–Ϋ―•–Ζ–Α―Ü―•―½ , –Ϋ–Α–Ω―Ä–Η–Κ–Μ–Α–¥, –¥–Μ―è –Ψ–Ϋ–Ψ–≤–Μ–Β–Ϋ–Ϋ―è –¥–Β―è–Κ–Η―Ö –Ζ–Φ―•–Ϋ–Ϋ–Η―Ö ―â–Ψ –¥―•–Μ―è―²―¨―¹―è –Φ―•–Ε –Ϋ–Η–Φ–Η. –ë–Β–Ζ ―¹–Η–Ϋ―Ö―Ä–Ψ–Ϋ―•–Ζ–Α―Ü―•―½ ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―½ –¥–≤–Ψ―Ö –Ϋ–Η―²–Ψ–Κ –Φ–Ψ–Ε―É―²―¨ ―΅–Β―Ä–≥―É–≤–Α―²–Η―¹―è ―É –±―É–¥―¨-―è–Κ–Ψ–Φ―É –Ω–Ψ―Ä―è–¥–Κ―É. –ù–Α–Ω―Ä–Η–Κ–Μ–Α–¥, ―Ö–Α–Ι –Φ–Α―î–Φ–Ψ ―²–Α–Κ―É –Ω―Ä–Ψ–≥―Ä–Α–Φ―É:

–ù–Η―²―¨ A

–ù–Η―²―¨ B

1A: –ü―Ä–Ψ―΅–Η―²–Α―²–Η –Ζ–Φ―•–Ϋ–Ϋ―É V

1B: –ü―Ä–Ψ―΅–Η―²–Α―²–Η –Ζ–Φ―•–Ϋ–Ϋ―É V

2A: –î–Ψ–¥–Α―²–Η 1 –¥–Ψ –Ζ–Φ―•–Ϋ–Ϋ–Ψ―½ V

2B: –î–Ψ–¥–Α―²–Η 1 –¥–Ψ –Ζ–Φ―•–Ϋ–Ϋ–Ψ―½ V

3A: –½–Α–Ω–Η―¹–Α―²–Η –Ϋ–Α–Ζ–Α–¥ ―É –Ζ–Φ―•–Ϋ–Ϋ―É V

3B: –½–Α–Ω–Η―¹–Α―²–Η –Ϋ–Α–Ζ–Α–¥ ―É –Ζ–Φ―•–Ϋ–Ϋ―É V

–·–Κ―â–Ψ ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―è 1B –≤–Η–Κ–Ψ–Ϋ–Α―î―²―¨―¹―è –Φ―•–Ε 1A ―²–Α 3A, ―΅–Η ―è–Κ―â–Ψ ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―è 1A –≤–Η–Κ–Ψ–Ϋ–Α―î―²―¨―¹―è –Φ―•–Ε 1B ―²–Α 3B, –Ω―Ä–Ψ–≥―Ä–Α–Φ–Α –±―É–¥–Β –Ω―Ä–Ψ–¥―É–Κ―É–≤–Α―²–Η –Ϋ–Β–Ω―Ä–Α–≤–Η–Μ―¨–Ϋ―• –¥–Α–Ϋ―•. –Π–Β –≤―•–¥–Ψ–Φ–Β ―è–Κ ―¹―²–Α–Ϋ –≥–Ψ–Ϋ–Η―²–≤–Η . –ü―Ä–Ψ–≥―Ä–Α–Φ―•―¹―² –Φ–Α―î –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É–≤–Α―²–Η –±–Μ–Ψ–Κ―É–≤–Α–Ϋ–Ϋ―è (–Α–Ϋ–≥–Μ. lock ) ―â–Ψ–± ―¹―²–≤–Ψ―Ä–Η―²–Η –≤–Ζ–Α―î–Φ–Ϋ–Β –≤–Η–Κ–Μ―é―΅–Β–Ϋ–Ϋ―è . –½–Α–Φ–Ψ–Κ βÄî ―Ü–Β –Κ–Ψ–Ϋ―¹―²―Ä―É–Κ―Ü―•―è –Φ–Ψ–≤–Η –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è, ―â–Ψ –¥–Ψ–Ζ–≤–Ψ–Μ―è―î –Ψ–¥–Ϋ―•–Ι –Ϋ–Η―²―• –Ψ―²―Ä–Η–Φ–Α―²–Η –Κ–Ψ–Ϋ―²―Ä–Ψ–Μ―¨ –Ϋ–Α–¥ –Ζ–Φ―•–Ϋ–Ϋ–Ψ―é ―• –Ζ–Α–Ω–Ψ–±―•–≥―²–Η ―΅–Η―²–Α–Ϋ–Ϋ―é ―΅–Η –Ζ–Α–Ω–Η―¹―É –≤ ―Ü―é –Ζ–Φ―•–Ϋ–Ϋ―É –≤―•–¥ ―•–Ϋ―à–Η―Ö –Ϋ–Η―²–Ψ–Κ, –Α–Ε –Ω–Ψ–Κ–Η ―Ü―è –Ζ–Φ―•–Ϋ–Ϋ–Α –Ϋ–Β –±―É–¥–Β ―Ä–Ψ–Ζ–±–Μ–Ψ–Κ–Ψ–≤–Α–Ϋ–Α. –ù–Η―²―¨ ―â–Ψ ―¹―²–≤–Ψ―Ä–Η–Μ–Α –Ζ–Α–Φ–Ψ–Κ –Φ–Ψ–Ε–Β –≤―•–Μ―¨–Ϋ–Ψ –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η ―¹–≤–Ψ―é –Κ―Ä–Η―²–Η―΅–Ϋ―É ―¹–Β–Κ―Ü―•―é (―¹–Β–Κ―Ü―•―é –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η ―â–Ψ –≤–Η–Φ–Α–≥–Α―î –Β–Κ―¹–Κ–Μ―é–Ζ–Η–≤–Ϋ–Ψ–≥–Ψ –¥–Ψ―¹―²―É–Ω―É –¥–Ψ –Ω–Β–≤–Ϋ–Ψ―½ –Ζ–Φ―•–Ϋ–Ϋ–Ψ―½), ―• ―Ä–Ψ–Ζ–±–Μ–Ψ–Κ―É–≤–Α―²–Η –¥–Α–Ϋ―• –Κ–Ψ–Μ–Η ―¹–Β–Κ―Ü―•―è –Ζ–Α–Κ―•–Ϋ―΅–Η―²―¨―¹―è. –Δ–Ψ–Φ―É, ―â–Ψ–± –≥–Α―Ä–Α–Ϋ―²―É–≤–Α―²–Η –Ω―Ä–Α–≤–Η–Μ―¨–Ϋ–Β –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è, –Ω―Ä–Ψ–≥―Ä–Α–Φ–Α –¥–Α–Ϋ–Α –≤–Η―â–Β –Φ–Ψ–Ε–Β –±―É―²–Η –Ω–Β―Ä–Β–Ω–Η―¹–Α–Ϋ–Α –Ζ –≤–Η–Κ–Ψ―Ä–Η―¹―²–Α–Ϋ–Ϋ―è–Φ –Ζ–Α–Φ–Κ―•–≤:

–ù–Η―²―¨ A

–ù–Η―²―¨ B

1A: –½–Α–Φ–Κ–Ϋ―É―²–Η –Ζ–Φ―•–Ϋ–Ϋ―É V

1B: –½–Α–Φ–Κ–Ϋ―É―²–Η –Ζ–Φ―•–Ϋ–Ϋ―É V

2A: –ü―Ä–Ψ―΅–Η―²–Α―²–Η –Ζ–Φ―•–Ϋ–Ϋ―É V

2B: –ü―Ä–Ψ―΅–Η―²–Α―²–Η –Ζ–Φ―•–Ϋ–Ϋ―É V

3A: –î–Ψ–¥–Α―²–Η 1 –¥–Ψ –Ζ–Φ―•–Ϋ–Ϋ–Ψ―½ V

3B: –î–Ψ–¥–Α―²–Η 1 –¥–Ψ –Ζ–Φ―•–Ϋ–Ϋ–Ψ―½ V

4A –½–Α–Ω–Η―¹–Α―²–Η –Ϋ–Α–Ζ–Α–¥ ―É –Ζ–Φ―•–Ϋ–Ϋ―É V

4B: –½–Α–Ω–Η―¹–Α―²–Η –Ϋ–Α–Ζ–Α–¥ ―É –Ζ–Φ―•–Ϋ–Ϋ―É V

5A: –†–Ψ–Ζ–±–Μ–Ψ–Κ―É–≤–Α―²–Η –Ζ–Φ―•–Ϋ–Ϋ―É V

5B: –†–Ψ–Ζ–±–Μ–Ψ–Κ―É–≤–Α―²–Η –Ζ–Φ―•–Ϋ–Ϋ―É V

–û–¥–Ϋ–Α –Ϋ–Η―²―¨ ―É―¹–Ω―•―à–Ϋ–Ψ –Ζ–Α–±–Μ–Ψ–Κ―É―î –Ζ–Φ―•–Ϋ–Ϋ―É V, –Ω–Ψ–Κ–Η ―•–Ϋ―à–Α –±―É–¥–Β –Ζ–Α–Φ–Κ–Ϋ–Β–Ϋ–Α βÄî –Ϋ–Β –Ζ–Φ–Ψ–Ε–Β –Ω―Ä–Ψ–¥–Ψ–≤–Ε–Η―²–Η ―Ä–Ψ–±–Ψ―²―É, –Ω–Ψ–Κ–Η V –Ϋ–Β ―Ä–Ψ–Ζ–±–Μ–Ψ–Κ―É―î―²―¨―¹―è. –Π–Β –≥–Α―Ä–Α–Ϋ―²―É–≤–Α―²–Η–Φ–Β –Ω―Ä–Α–≤–Η–Μ―¨–Ϋ–Β –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η. –½–Α–Φ–Κ–Η –Ϋ–Β–Ψ–±―Ö―•–¥–Ϋ―• ―â–Ψ–± –≥–Α―Ä–Α–Ϋ―²―É–≤–Α―²–Η –Κ–Ψ―Ä–Β–Κ―²–Ϋ–Β –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η, –Α–Μ–Β –Φ–Ψ–Ε―É―²―¨ ―¹–Η–Μ―¨–Ϋ–Ψ ―½―½ ―¹–Ω–Ψ–≤―•–Μ―¨–Ϋ–Η―²–Η.

–ë–Μ–Ψ–Κ―É–≤–Α–Ϋ–Ϋ―è –±–Α–≥–Α―²―¨–Ψ―Ö –Ζ–Φ―•–Ϋ–Ϋ–Η―Ö –Ζ –≤–Η–Κ–Ψ―Ä–Η―¹―²–Α–Ϋ–Ϋ―è–Φ –Ϋ–Β–Α―²–Ψ–Φ–Α―Ä–Ϋ–Η―Ö –Ζ–Α–Φ–Κ―•–≤ ―¹―²–≤–Ψ―Ä―é―î –Φ–Ψ–Ε–Μ–Η–≤―•―¹―²―¨ –≤–Ζ–Α―î–Φ–Ϋ–Ψ–≥–Ψ –±–Μ–Ψ–Κ―É–≤–Α–Ϋ–Ϋ―è. –ê―²–Ψ–Φ–Α―Ä–Ϋ–Η–Ι –Ζ–Α–Φ–Ψ–Κ –Ζ–Α–Φ–Η–Κ–Α―î –≤―¹―• –Ζ–Φ―•–Ϋ–Ϋ―• –Ζ–Α ―Ä–Α–Ζ. –·–Κ―â–Ψ –≤―•–Ϋ –Ϋ–Β –Φ–Ψ–Ε–Β –Ζ–Α–Φ–Κ–Ϋ―É―²–Η –≤―¹―• –Ζ –Ϋ–Η―Ö, –≤―•–Ϋ –Ϋ–Β –Ζ–Α–Φ–Η–Κ–Α―î –Ε–Ψ–¥–Ϋ–Ψ―½. –·–Κ―â–Ψ –¥–≤―• –Ϋ–Η―²―• –Ω–Ψ―²―Ä–Β–±―É―é―²―¨ –Ζ–Α–Φ–Κ–Ϋ―É―²–Η –Ψ–¥–Ϋ–Α–Κ–Ψ–≤―• –¥–≤―• –Ζ–Φ―•–Ϋ–Ϋ―• –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―΅–Η –Ϋ–Β–Α―²–Ψ–Φ–Α―Ä–Ϋ―• –Ζ–Α–Φ–Κ–Η, –Φ–Ψ–Ε–Μ–Η–≤–Η–Ι –≤–Η–Ω–Α–¥–Ψ–Κ –Κ–Ψ–Μ–Η –Ψ–¥–Ϋ–Α –Ϋ–Η―²―¨ –Ζ–Α–Φ–Η–Κ–Α―î –Ψ–¥–Ϋ―É –Ζ–Φ―•–Ϋ–Ϋ―É, –Α ―•–Ϋ―à–Α –¥―Ä―É–≥―É. –£ ―²–Α–Κ–Ψ–Φ―É –≤–Η–Ω–Α–¥–Κ―É –Ε–Ψ–¥–Ϋ–Α –Ζ –Ϋ–Η―²–Β–Ι –Ϋ–Β –Φ–Ψ–Ε–Β –Ω―Ä–Ψ–¥–Ψ–≤–Ε―É–≤–Α―²–Η ―Ä–Ψ–±–Ψ―²―É, ―â–Ψ –Ω―Ä–Η–≤–Ψ–¥–Η―²―¨ –¥–Ψ –≤–Ζ–Α―î–Φ–Ϋ–Ψ–≥–Ψ –±–Μ–Ψ–Κ―É–≤–Α–Ϋ–Ϋ―è.

–ë–Α–≥–Α―²–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Ω―Ä–Ψ–≥―Ä–Α–Φ –≤–Η–Φ–Α–≥–Α―é―²―¨ ―²–Ψ–≥–Ψ, ―â–Ψ–± ―½―Ö–Ϋ―• –Ω―•–¥–Ζ–Α–¥–Α―΅―• –≤–Η–Κ–Ψ–Ϋ―É–≤–Α–Μ–Η―¹―¨ ―¹–Η–Ϋ―Ö―Ä–Ψ–Ϋ–Ϋ–Ψ . –Π–Β –Ω–Ψ―²―Ä–Β–±―É―î –≤–Η–Κ–Ψ―Ä–Η―¹―²–Α–Ϋ–Ϋ―è –±–Α―Ä'―î―Ä–Α . –ë–Α―Ä'―î―Ä–Η –Ζ–Α–Ζ–≤–Η―΅–Α–Ι ―Ä–Β–Α–Μ―•–Ζ―É―é―²―¨―¹―è –Ζ –≤–Η–Κ–Ψ―Ä–Η―¹―²–Α–Ϋ–Ϋ―è–Φ –Ω―Ä–Ψ–≥―Ä–Α–Φ–Ϋ–Ψ–≥–Ψ –Ζ–Α–Φ–Κ–Α. –û–¥–Η–Ϋ –Κ–Μ–Α―¹ –Α–Μ–≥–Ψ―Ä–Η―²–Φ―•–≤, ―â–Ψ –≤―•–¥–Ψ–Φ―• –Ω―•–¥ –Ϋ–Α–Ζ–≤–Ψ―é –±–Β–Ζ–Ζ–Α–Φ–Κ–Ψ–≤―• ―²–Α –±–Β–Ζ–Ζ―É–Ω–Η–Ϋ–Κ–Ψ–≤―• –Α–Μ–≥–Ψ―Ä–Η―²–Φ–Η (–Α–Ϋ–≥–Μ. lack-free and wait-free algorithms ), ―É–Ϋ–Η–Κ–Α―é―²―¨ –≤–Η–Κ–Ψ―Ä–Η―¹―²–Α–Ϋ–Ϋ―è –Ζ–Α–Φ–Κ―•–≤ ―²–Α –±–Α―Ä'―î―Ä―•–≤. –ü―Ä–Α–≤–¥–Α ―²–Α–Κ–Η–Ι –Ω―•–¥―Ö―•–¥ –Ζ–Α–Ζ–≤–Η―΅–Α–Ι –≤–Α–Ε–Κ–Ψ ―Ä–Β–Α–Μ―•–Ζ―É–≤–Α―²–Η ―• –≤–Η–Φ–Α–≥–Α―î –Ω―Ä–Α–≤–Η–Μ―¨–Ϋ–Ψ ―¹–Κ–Ψ–Ϋ―¹―²―Ä―É–Ι–Ψ–≤–Α–Ϋ–Η―Ö ―¹―²―Ä―É–Κ―²―É―Ä –¥–Α–Ϋ–Η―Ö.

–ù–Β –Κ–Ψ–Ε–Ϋ–Β ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é–≤–Α–Ϋ–Ϋ―è ―¹–Ω―Ä–Η―΅–Η–Ϋ―é―î –Ω―Ä–Η―¹–Κ–Ψ―Ä–Β–Ϋ–Ϋ―è. –½–Α–≥–Α–Μ–Ψ–Φ, –Κ–Ψ–Μ–Η –Ζ–Α–¥–Α―΅–Α ―Ä–Ψ–Ζ–±–Η–≤–Α―î―²―¨―¹―è –Ϋ–Α –±―•–Μ―¨―à–Β ―²–Α –±―•–Μ―¨―à–Β –Ϋ–Η―²–Ψ–Κ, ―²―• –Ϋ–Η―²–Κ–Η –≤–Η―²―Ä–Α―΅–Α―é―²―¨ –≤―¹–Β –±―•–Μ―¨―à–Β ―• –±―•–Μ―¨―à–Β ―΅–Α―¹―É –Ϋ–Α –Κ–Ψ–Φ―É–Ϋ―•–Κ–Α―Ü―•―½ –Φ―•–Ε ―¹–Ψ–±–Ψ―é. –½―Ä–Β―à―²–Ψ―é, ―΅–Α―¹ –Ϋ–Α –Κ–Ψ–Φ―É–Ϋ―•–Κ–Α―Ü―•―é –Ω–Β―Ä–Β–≤–Α–Ε–Α―î ―΅–Α―¹, ―â–Ψ –≤–Η―²―Ä–Α―΅–Α―î―²―¨―¹―è –Ϋ–Α ―Ä–Ψ–Ζ–≤'―è–Ζ–Α–Ϋ–Ϋ―è –Ζ–Α–¥–Α―΅―•, ―• –Ω–Ψ–¥–Α–Μ―¨―à–Β ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é–≤–Α–Ϋ–Ϋ―è (–Ω–Ψ–¥―•–Μ –Ϋ–Α ―â–Β –±―•–Μ―¨―à―É –Κ―•–Μ―¨–Κ―•―¹―²―¨ –Ϋ–Η―²–Ψ–Κ) ―¹–Κ–Ψ―Ä―•―à–Β –Ζ–±―•–Μ―¨―à―É―î –Α–Ϋ―•–Ε –Ζ–Φ–Β–Ϋ―à―É―î –Ω―Ä–Ψ―²―è–Ε–Ϋ―•―¹―²―¨ ―΅–Α―¹―É –Ω–Ψ―²―Ä―•–±–Ϋ–Ψ–≥–Ψ ―â–Ψ–± –Ζ–Α–Κ―•–Ϋ―΅–Η―²–Η ―Ä–Ψ–±–Ψ―²―É. –Π–Β –≤―•–¥–Ψ–Φ–Β ―è–Κ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Β ―¹–Ω–Ψ–≤―•–Μ―¨–Ϋ–Β–Ϋ–Ϋ―è .

–ü―Ä–Ψ–≥―Ä–Α–Φ–Η ―΅–Α―¹―²–Ψ –Κ–Μ–Α―¹–Η―³―•–Κ―É―é―²―¨―¹―è –≤―•–¥–Ω–Ψ–≤―•–¥–Ϋ–Ψ –¥–Ψ ―²–Ψ–≥–Ψ, ―è–Κ ―΅–Α―¹―²–Ψ ―½―Ö–Ϋ―• –Ω―•–¥–Ζ–Α–¥–Α―΅―• –Φ–Α―é―²―¨ ―¹–Η–Ϋ―Ö―Ä–Ψ–Ϋ―•–Ζ―É–≤–Α―²–Η―¹―¨ ―΅–Η ―¹–Ω―•–Μ–Κ―É–≤–Α―²–Η―¹―¨ –Ψ–¥–Η–Ϋ –Ζ –Ψ–¥–Ϋ–Η–Φ. –ü―Ä–Ψ–≥―Ä–Α–Φ–Α –Ω―Ä–Ψ―è–≤–Μ―è―î –¥―Ä―•–±–Ϋ–Ψ–Ζ–Β―Ä–Ϋ–Η―¹―²–Η–Ι –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ ―è–Κ―â–Ψ ―½―½ –Ω―•–¥–Ζ–Α–¥–Α―΅―• –Φ–Α―é―²―¨ –Ψ–±–Φ―•–Ϋ―é–≤–Α―²–Η―¹―¨ –¥–Α–Ϋ–Η–Φ–Η –±–Α–≥–Α―²–Ψ ―Ä–Α–Ζ―•–≤ –Ϋ–Α ―¹–Β–Κ―É–Ϋ–¥―É; –≤–Ψ–Ϋ–Α –Ω―Ä–Ψ―è–≤–Μ―è―î –Κ―Ä―É–Ω–Ϋ–Ψ–Ζ–Β―Ä–Ϋ–Η―¹―²–Η–Ι –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ, ―è–Κ―â–Ψ –≤–Ψ–Ϋ–Η –Ϋ–Β –Φ―É―¹―è―²―¨ –Ψ–±–Φ―•–Ϋ―é–≤–Α―²–Η―¹―¨ –¥–Α–Ϋ–Η–Φ–Η –±–Α–≥–Α―²–Ψ ―Ä–Α–Ζ―•–≤ –Ϋ–Α ―¹–Β–Κ―É–Ϋ–¥―É, ―• –≤–Ψ–Ϋ–Α –Ω―Ä–Ψ―è–≤–Μ―è―î –Ω―Ä–Η–≥–Ψ–Μ–Ψ–Φ―à–Μ–Η–≤–Η–Ι –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ, ―è–Κ―â–Ψ –≤–Ψ–Ϋ–Η ―Ä―•–¥–Κ–Ψ, ―΅–Η –≤–Ζ–Α–≥–Α–Μ―• –Ϋ―•–Κ–Ψ–Μ–Η –Ϋ–Β –Φ–Α―é―²―¨ –Ψ–±–Φ―•–Ϋ―é–≤–Α―²–Η―¹―¨ –¥–Α–Ϋ–Η–Φ–Η. –ü―Ä–Η–≥–Ψ–Μ–Ψ–Φ―à–Μ–Η–≤–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –≤–≤–Α–Ε–Α―é―²―¨―¹―è ―²–Α–Κ–Η–Φ–Η ―â–Ψ ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é―é―²―¨―¹―è –Ϋ–Α–Ι–Μ–Β–≥―à–Β.

–ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Φ–Ψ–≤–Η –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è ―²–Α –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Η –Φ–Α―é―²―¨ –Φ–Α―²–Η –Φ–Ψ–¥–Β–Μ―¨ ―É–Ζ–≥–Ψ–¥–Ε–Β–Ϋ–Ψ―¹―²―• (―²–Α–Κ–Ψ–Ε –≤―•–¥–Ψ–Φ―É ―è–Κ –Φ–Ψ–¥–Β–Μ―¨ –Ω–Α–Φ'―è―²―•). –€–Ψ–¥–Β–Μ―¨ ―É–Ζ–≥–Ψ–¥–Ε–Β–Ϋ–Ψ―¹―²―• –Ψ–Ω–Η―¹―É―î –Ω―Ä–Α–≤–Η–Μ–Α –Ω―Ä–Ψ–≤–Β–¥–Β–Ϋ–Ϋ―è ―Ä―•–Ζ–Ϋ–Ψ–Φ–Α–Ϋ―•―²–Ϋ–Η―Ö –Ψ–Ω–Β―Ä–Α―Ü―•–Ι –Ζ –Ω–Α–Φ'―è―²―²―é, ―²–Α ―â–Ψ –Φ–Η –Ψ―²―Ä–Η–Φ―É―î–Φ–Ψ –≤ ―Ä–Β–Ζ―É–Μ―¨―²–Α―²―• ―Ü–Η―Ö –Ψ–Ω–Β―Ä–Α―Ü―•–Ι.

–û–¥–Ϋ―•―î―é –Ζ –Ω–Β―Ä―à–Η―Ö –Φ–Ψ–¥–Β–Μ–Β–Ι ―É–Ζ–≥–Ψ–¥–Ε–Β–Ϋ–Ψ―¹―²―• –±―É–Μ–Α –Φ–Ψ–¥–Β–Μ―¨ –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Ψ―½ ―â―•–Μ―¨–Ϋ–Ψ―¹―²―• –¦–Β―¹–Μ―• –¦–Α–Φ–Ω–Ψ―Ä―²–Α . –ü–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Α ―É–Ζ–≥–Ψ–¥–Ε–Β–Ϋ―•―¹―²―¨ βÄî ―Ü–Β –≤–Μ–Α―¹―²–Η–≤―•―¹―²―¨ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ―½ –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –¥–Α–≤–Α―²–Η ―²–Α–Κ–Η–Ι ―¹–Α–Φ–Η–Ι ―Ä–Β–Ζ―É–Μ―¨―²–Α―² ―â–Ψ ―• ―½―½ –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Η–Ι –Α–Ϋ–Α–Μ–Ψ–≥. –ö–Ψ–Ϋ–Κ―Ä–Β―²–Ϋ―•―à–Β, –Ω―Ä–Ψ–≥―Ä–Α–Φ–Α –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Ψ ―É–Ζ–≥–Ψ–¥–Ε–Β–Ϋ–Α, ―è–Κ―â–Ψ "βÄΠ ―Ä–Β–Ζ―É–Μ―¨―²–Α―² –±―É–¥―¨-―è–Κ–Ψ–≥–Ψ –Ζ–Α–Ω―É―¹–Κ―É ―²–Α–Κ–Η–Ι ―¹–Α–Φ–Η–Ι, ―è–Κ –±―É–≤ –±–Η ―è–Κ―â–Ψ –Ψ–Ω–Β―Ä–Α―Ü―•―½ –Ϋ–Α –Κ–Ψ–Ε–Ϋ–Ψ–Φ―É –Ψ–Κ―Ä–Β–Φ–Ψ–Φ―É –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―• –≤–Η–Κ–Ψ–Ϋ―É–≤–Α–Μ–Η―¹―¨ ―²–Α–Κ, –Ϋ―•–±–Η –≤–Ψ–Ϋ–Η –≤–Η–Κ–Ψ–Ϋ―É―é―²―¨―¹―è –≤ –Ω–Β–≤–Ϋ―•–Ι –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Ψ―¹―²―• –Ζ–Α–¥–Α–Ϋ―•–Ι –Ω―Ä–Ψ–≥―Ä–Α–Φ–Ψ―é.[ 16]

–Δ―Ä–Α–Ϋ–Ζ–Α–Κ―Ü―•–Ι–Ϋ–Α –Ω–Α–Φ'―è―²―¨ ―Ü–Β ―²–Η–Ω–Ψ–≤–Η–Ι –Ω―Ä–Η–Κ–Μ–Α–¥ –Φ–Ψ–¥–Β–Μ―• ―É–Ζ–≥–Ψ–¥–Ε–Β–Ϋ–Ψ―¹―²―•. –Δ―Ä–Α–Ϋ–Ζ–Α–Κ―Ü―•–Ι–Ϋ–Α –Ω–Α–Φ'―è―²―¨ –≤–Ζ―è–Μ–Α ―É ―²–Β–Ψ―Ä―•―½ –±–Α–Ζ –¥–Α–Ϋ–Η―Ö –Ω―Ä–Η–Ϋ―Ü–Η–Ω –Α―²–Ψ–Φ–Α―Ä–Ϋ–Ψ―½ ―²―Ä–Α–Ϋ–Ζ–Α–Κ―Ü―•―½ ―²–Α –Ζ–Α―¹―²–Ψ―¹―É–≤–Α–Μ–Α –Ι–Ψ–≥–Ψ –Ω―Ä–Η –¥–Ψ―¹―²―É–Ω―• –¥–Ψ –Ω–Α–Φ'―è―²―•.

–€–Α―²–Β–Φ–Α―²–Η―΅–Ϋ–Ψ, ―Ü―• –Φ–Ψ–¥–Β–Μ―• –Φ–Ψ–Ε―É―²―¨ –Ω―Ä–Β–¥―¹―²–Α–≤–Μ―è―²–Η―¹―¨ –Κ―•–Μ―¨–Κ–Ψ–Φ–Α ―¹–Ω–Ψ―¹–Ψ–±–Α–Φ–Η. –€–Β―Ä–Β–Ε―• –ü–Β―²―Ä―• , ―â–Ψ –±―É–Μ–Η –≤–Ω–Β―Ä―à–Β –Ω―Ä–Β–¥―¹―²–Α–≤–Μ–Β–Ϋ―• –ö–Α―Ä–Μ–Ψ–Φ –ê–¥–Α–Φ–Ψ–Φ –ü–Β―²―Ä―• ―É 1962-–≥–Ψ–Φ―É, –±―É–Μ–Η ―Ä–Α–Ϋ–Ϋ―•–Φ–Η ―¹–Ω―Ä–Ψ–±–Α–Φ–Η ―¹–Η―¹―²–Β–Φ–Α―²–Η–Ζ―É–≤–Α―²–Η –Ω―Ä–Α–≤–Η–Μ–Α ―É–Ζ–≥–Ψ–¥–Ε–Β–Ϋ–Ψ―¹―²―• –Φ–Ψ–¥–Β–Μ–Β–Ι. –ù–Α ―½―Ö–Ϋ―•–Ι –Ψ―¹–Ϋ–Ψ–≤―• –Ω–Ψ–±―É–¥–Ψ–≤–Α–Ϋ–Α ―²–Β–Ψ―Ä―•―è –Ω–Ψ―²–Ψ–Κ―•–≤ –¥–Α–Ϋ–Η―Ö, –Α ―½―Ö–Ϋ―è –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä–Α –±―É–Μ–Α ―¹―²–≤–Ψ―Ä–Β–Ϋ–Α, ―â–Ψ–± ―Ä–Β–Α–Μ―•–Ζ―É–≤–Α―²–Η ―•–¥–Β―½ ―Ü―•―î―½ ―²–Β–Ψ―Ä―•―½ ―³―•–Ζ–Η―΅–Ϋ–Ψ. –ü–Ψ―΅–Η–Ϋ–Α―é―΅–Η –Ζ –Κ―•–Ϋ―Ü―è 1970-―Ö, –±―É–Μ–Η ―Ä–Ψ–Ζ―Ä–Ψ–±–Μ–Β–Ϋ―• ―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ―Ü–Β―¹―•–≤ , ―²–Α–Κ―• ―è–Κ –ß–Η―¹–Μ–Β–Ϋ–Ϋ―è –Γ–Η―¹―²–Β–Φ, ―â–Ψ –Γ–Ω―•–Μ–Κ―É―é―²―¨―¹―è ―²–Α –ü–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ―• –ü―Ä–Ψ―Ü–Β―¹–Η, ―â–Ψ –Γ–Ω―•–Μ–Κ―É―é―²―¨―¹―è , ―â–Ψ–± ―É–Φ–Ψ–Ε–Μ–Η–≤–Η―²–Η –Α–Μ–≥–Β–±―Ä–Α―½―΅–Ϋ–Β –Ψ–±“ë―Ä―É–Ϋ―²―É–≤–Α–Ϋ–Ϋ―è ―¹–Η―¹―²–Β–Φ ―¹–Κ–Μ–Α–¥–Β–Ϋ–Η―Ö –Ζ –≤–Ζ–Α―î–Φ–Ψ–¥―•―é―΅–Η―Ö –Κ–Ψ–Φ–Ω–Ψ–Ϋ–Β–Ϋ―²―•–≤. –ù–Ψ–≤―•―à―• –¥–Ψ–Ω–Ψ–≤–Ϋ–Β–Ϋ–Ϋ―è –¥–Ψ ―¹―•–Φ'―½ ―΅–Η―¹–Μ–Β–Ϋ―¨ –Ω―Ä–Ψ―Ü–Β―¹―•–≤, ―²–Α–Κ―• ―è–Κ œÄ-―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è , –¥–Ψ–¥–Α–Μ–Η –Φ–Ψ–Ε–Μ–Η–≤―•―¹―²―¨ –Ψ–±“ë―Ä―É–Ϋ―²―É–≤–Α–Ϋ–Ϋ―è –¥–Η–Ϋ–Α–Φ―•―΅–Ϋ–Η―Ö ―²–Ψ–Ω–Ψ–Μ–Ψ–≥―•–Ι. –Δ–Α–Κ―• –Μ–Ψ–≥―•–Κ–Η ―è–Κ TLA+ , ―²–Α –Φ–Α―²–Β–Φ–Α―²–Η―΅–Ϋ―• –Φ–Ψ–¥–Β–Μ―• ―²–Α–Κ―• ―è–Κ ―²―Ä–Α―¹–Η ―²–Α –¥―•–Α–≥―Ä–Α–Φ–Η –Ω–Ψ–¥―•–Ι –Α–Κ―²–Ψ―Ä–Α , ―²–Α–Κ–Ψ–Ε –±―É–Μ–Η ―Ä–Ψ–Ζ–≤–Η–Ϋ–Β–Ϋ―• ―â–Ψ–± –Ψ–Ω–Η―¹–Α―²–Η –Ω–Ψ–≤–Β–¥―•–Ϋ–Κ―É –Κ–Ψ–Ϋ–Κ―É―Ä–Β–Ϋ―²–Ϋ–Η―Ö ―¹–Η―¹―²–Β–Φ.

–€–Α–Ι–Κ–Μ –î–Ε. –Λ–Μ―•–Ϋ–Ϋ ―¹―²–≤–Ψ―Ä–Η–≤ –Ψ–¥–Ϋ―É –Ζ –Ϋ–Α–Ι–Ω–Β―Ä―à–Η―Ö –Κ–Μ–Α―¹–Η―³―•–Κ–Α―Ü―•–Ι ―¹–Η―¹―²–Β–Φ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö (―²–Α –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Η―Ö) –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤ ―²–Α –Ω―Ä–Ψ–≥―Ä–Α–Φ, ―â–Ψ –Ϋ–Η–Ϋ―• –≤―•–¥–Ψ–Φ–Α ―è–Κ –Δ–Α–Κ―¹–Ψ–Ϋ–Ψ–Φ―•―è –Λ–Μ―•–Ϋ–Ϋ–Α . –Λ–Μ―•–Ϋ–Ϋ –Ω–Ψ–¥―•–Μ―è–≤ –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η ―²–Α –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Α–Φ–Η –Ζ–Α–Μ–Β–Ε–Ϋ–Ψ –≤―•–¥ ―²–Ψ–≥–Ψ ―΅–Η –≤–Ψ–Ϋ–Η –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É–≤–Α–Μ–Η –Ψ–¥–Η–Ϋ ―΅–Η –±–Α–≥–Α―²–Ψ –Ω–Ψ―²–Ψ–Κ―•–≤ –Κ–Ψ–Φ–Α–Ϋ–¥, ―²–Α ―΅–Η –Κ–Ψ–Φ–Α–Ϋ–¥–Η –Ψ–Ω–Β―Ä―É–≤–Α–Μ–Η –Ψ–¥–Ϋ–Η–Φ ―΅–Η –±–Α–≥–Α―²―¨–Φ–Α –Φ–Ϋ–Ψ–Ε–Η–Ϋ–Α–Φ–Η –¥–Α–Ϋ–Η―Ö.

–ö–Μ–Α―¹–Η―³―•–Κ–Α―Ü―•―è –Λ–Μ―•–Ϋ–Ϋ–Α

–û–¥–Η–Ϋ–Ψ―΅–Ϋ–Η–Ι Single Instruction

–€–Ϋ–Ψ–Ε–Η–Ϋ–Ϋ–Η–Ι Multiple Instruction

–û–¥–Η–Ϋ–Ψ―΅–Ϋ–Η–Ι Single Data

SISD

MISD

–€–Ϋ–Ψ–Ε–Η–Ϋ–Ϋ–Η–Ι Multiple Data

SIMD

MIMD

–ö–Μ–Α―¹ single-instruction-single-data (SISD) –Β–Κ–≤―•–≤–Α–Μ–Β–Ϋ―²–Ϋ–Η–Ι ―Ü―•–Μ–Κ–Ψ–≤–Η―²–Ψ –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ―•–Ι –Ω―Ä–Ψ–≥―Ä–Α–Φ―•. Single-instruction-multiple-data (SIMD) –Β–Κ–≤―•–≤–Α–Μ–Β–Ϋ―²–Ϋ–Η–Ι –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―é –Ψ–¥–Ϋ―•―î―½ ―²–Α ―²―•―î―½ –Ε –Ψ–Ω–Β―Ä–Α―Ü―•―½ –Ω–Ψ–≤―²–Ψ―Ä―é–≤–Α–Ϋ–Ψ –Ϋ–Α–¥ –≤–Β–Μ–Η–Κ–Η–Φ –Φ–Α―¹–Η–≤–Ψ–Φ –¥–Α–Ϋ–Η―Ö. –Π–Β –Ζ–Α–Ζ–≤–Η―΅–Α–Ι –≤―•–¥–±―É–≤–Α―î―²―¨―¹―è ―É –Ζ–Α–¥–Α―΅–Α―Ö –Ψ–±―Ä–Ψ–±–Κ–Η ―¹–Η–≥–Ϋ–Α–Μ―•–≤ . –ö–Μ–Α―¹ Multiple-instruction-single-data (MISD) –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―î―²―¨―¹―è ―Ä―•–¥–Κ–Ψ. –ü–Ψ–Κ–Η –Ω―Ä–Η–¥―É–Φ―É–≤–Α–Μ–Η―¹―¨ –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä–Η, ―â–Ψ ―¹―²–Ψ―¹―É―é―²―¨―¹―è ―Ü―¨–Ψ–≥–Ψ –Κ–Μ–Α―¹―É (―è–Κ –Ϋ–Α–Ω―Ä–Η–Κ–Μ–Α–¥ ―¹–Η―¹―²–Ψ–Μ―•―΅–Ϋ―• –Φ–Α―¹–Η–≤–Η ), –Ζ'―è–≤–Η–Μ–Ψ―¹―¨ –Μ–Η―à–Β –Κ―•–Μ―¨–Κ–Α –Ω―Ä–Ψ–≥―Ä–Α–Φ, ―â–Ψ –Ω―•–¥–Ω–Α–¥–Α―é―²―¨ –Ω―•–¥ ―Ü–Β–Ι –Κ–Μ–Α―¹. Multiple-instruction-multiple-data (MIMD) –Ϋ–Α–Ι―²–Η–Ω–Ψ–≤―•―à―• –Ω―Ä–Β–¥―¹―²–Α–≤–Ϋ–Η–Κ–Η –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Ω―Ä–Ψ–≥―Ä–Α–Φ.

–½–≥―•–¥–Ϋ–Ψ –Ζ –î–Β–≤―•–¥–Ψ–Φ –ü–Α―²―²–Β―Ä―¹–Ψ–Ϋ–Ψ–Φ ―²–Α –î–Ε–Ψ–Ϋ–Ψ–Φ –™–Β–Ϋ–Ϋ–Β―¹―•, ¬Ϊ–î–Β―è–Κ―• –Φ–Α―à–Η–Ϋ–Η ―î –≥―•–±―Ä–Η–¥–Α–Φ–Η ―Ü–Η―Ö –Κ–Α―²–Β–≥–Ψ―Ä―•–Ι, ―â–Ψ–Ω―Ä–Α–≤–¥–Α ―Ü―è –Κ–Μ–Α―¹–Η―΅–Ϋ–Α –Φ–Ψ–¥–Β–Μ―¨ –≤–Η–Ε–Η–Μ–Α ―΅–Β―Ä–Β–Ζ ―²–Β, ―â–Ψ –≤–Ψ–Ϋ–Α –Ω―Ä–Ψ―¹―²–Α, –Μ–Β–≥–Κ–Α –¥–Μ―è ―Ä–Ψ–Ζ―É–Φ―•–Ϋ–Ϋ―è, ―²–Α –¥–Α―î –≥–Α―Ä–Ϋ–Β –Ω–Β―Ä―à–Β –Ϋ–Α–±–Μ–Η–Ε–Β–Ϋ–Ϋ―è. –£–Ψ–Ϋ–Α ―²–Α–Κ–Ψ–Ε, –Φ–Ψ–Ε–Μ–Η–≤–Ψ ―΅–Β―Ä–Β–Ζ ―½―½ –Ζ―Ä–Ψ–Ζ―É–Φ―•–Μ―•―¹―²―¨ βÄî –Ϋ–Α–Ι–Ω–Ψ―à–Η―Ä–Β–Ϋ―•―à–Α ―¹―Ö–Β–Φ–Α.¬Μ[ 17]

–½ –≤–Η–Ϋ–Α–Ι–¥–Β–Ϋ–Ϋ―è–Φ ―É 1970-―²–Η―Ö ―²–Β―Ö–Ϋ–Ψ–Μ–Ψ–≥―•―½ ―¹―²–≤–Ψ―Ä–Β–Ϋ–Ϋ―è –Ϋ–Α–¥–≤–Β–Μ–Η–Κ–Η―Ö ―•–Ϋ―²–Β–≥―Ä–Α–Μ―¨–Ϋ–Η―Ö ―¹―Ö–Β–Φ –Ω―Ä–Η―¹–Κ–Ψ―Ä–Β–Ϋ–Ϋ―è –≤ –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ―•–Ι –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä―• –≤―•–¥–±―É–≤–Α–Μ–Ψ―¹―¨ –Ζ –¥–Ψ–Ω–Ψ–Φ–Ψ–≥–Ψ―é –Ω–Ψ–¥–≤–Ψ―î–Ϋ–Ϋ―è ―Ä–Ψ–Ζ–Φ―•―Ä―É –Φ–Α―à–Η–Ϋ–Ϋ–Ψ–≥–Ψ ―¹–Μ–Ψ–≤–Α βÄî –Κ―•–Μ―¨–Κ–Ψ―¹―²―• ―•–Ϋ―³–Ψ―Ä–Φ–Α―Ü―•―½, ―è–Κ―É –Κ–Ψ–Φ–Ω'―é―²–Β―Ä –Φ–Ψ–Ε–Β –Ψ–±―Ä–Ψ–±–Μ―è―²–Η –Ζ–Α –Ψ–¥–Η–Ϋ ―Ü–Η–Κ–Μ.[ 18] –≤–Ψ―¹―¨–Φ–Η–±―•―²–Ϋ–Η–Ι –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä –Φ–Α―î –¥–Ψ–¥–Α―²–Η –¥–≤–Α ―à―•―¹―²–Ϋ–Α–¥―Ü―è―²–Η―Ä–Ψ–Ζ―Ä―è–¥–Ϋ―• ―΅–Η―¹–Μ–Α, –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä –Φ–Α―î ―¹–Ω–Ψ―΅–Α―²–Κ―É –¥–Ψ–¥–Α―²–Η 8 –±―•―² –Ϋ–Η–Ε―΅–Ψ–≥–Ψ ―Ä–Ψ–Ζ―Ä―è–¥―É –Ζ –Κ–Ψ–Ε–Ϋ–Ψ–≥–Ψ ―΅–Η―¹–Μ–Α, –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―΅–Η ―¹―²–Α–Ϋ–¥–Α―Ä―²–Ϋ―É ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―é –¥–Ψ–¥–Α–≤–Α–Ϋ–Ϋ―è, –Ω–Ψ―²―•–Φ –¥–Ψ–¥–Α―²–Η 8 –±―•―²―•–≤ –≤–Η―â–Ψ–≥–Ψ ―Ä–Ψ–Ζ―Ä―è–¥―É, –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―΅–Η ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―é –¥–Ψ–¥–Α–≤–Α–Ϋ–Ϋ―è –Ζ –Ω–Β―Ä–Β–Ϋ–Ψ―¹–Ψ–Φ ―²–Α –±―•―² –Ω–Β―Ä–Β–Ϋ–Ψ―¹―É –≤―•–¥ –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –Ω–Ψ–Ω–Β―Ä–Β–¥–Ϋ―¨–Ψ–≥–Ψ –¥–Ψ–¥–Α–≤–Α–Ϋ–Ϋ―è. –Δ–Ψ–Φ―É –≤–Ψ―¹―¨–Φ–Η–±―•―²–Ϋ–Η–Ι –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä –Ω–Ψ―²―Ä–Β–±―É―î –¥–≤―• ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―½ –¥–Μ―è –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –Ψ–¥–Ϋ―•―î―½ –Ψ–Ω–Β―Ä–Α―Ü―•―½, –≤ ―²–Ψ–Ι ―΅–Α―¹ ―è–Κ ―à―•―¹―²–Ϋ–Α–¥―Ü―è―²–Η–±―•―²–Ϋ–Η–Ι –Μ–Η―à –Ψ–¥–Ϋ―É.

–Ü―¹―²–Ψ―Ä–Η―΅–Ϋ–Ψ, ―΅–Ψ―²–Η―Ä―¨–Ψ―Ö―Ä–Ψ–Ζ―Ä―è–¥–Ϋ―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Η –±―É–Μ–Η –Ζ–Α–Φ―•–Ϋ–Β–Ϋ―• –Ϋ–Α –≤–Ψ―¹―¨–Φ–Η―Ä–Ψ–Ζ―Ä―è–¥–Ϋ―• , –Ω–Ψ―²―•–Φ –Ϋ–Α ―à―•―¹―²–Ϋ–Α–¥―Ü―è―²–Η―Ä–Ψ–Ζ―Ä―è–¥–Ϋ―• , –Ω–Ψ―²―•–Φ –Ϋ–Α 32-―Ö ―Ä–Ψ–Ζ―Ä―è–¥–Ϋ―• . –Π―è ―²–Β–Ϋ–¥–Β–Ϋ―Ü―•―è –Ω―Ä–Η–Ω–Η–Ϋ–Η–Μ–Α―¹―¨ –Ζ –≤–≤–Β–¥–Β–Ϋ–Ϋ―è–Φ ―²―Ä–Η–¥―Ü―è―²–Η–¥–≤–Ψ―Ö―Ä–Ψ–Ζ―Ä―è–¥–Ϋ–Η―Ö –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤, ―è–Κ―• ―¹―²–Α–Μ–Η ―¹―²–Α–Ϋ–¥–Α―Ä―²–Ψ–Φ –¥–Μ―è –Ω–Β―Ä―¹–Ψ–Ϋ–Α–Μ―¨–Ϋ–Η―Ö –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤ –Ϋ–Α –¥–≤–Α –¥–Β―¹―è―²–Η–Μ―•―²―²―è. –ê–Ε –Ω–Ψ–Κ–Η –Ϋ–Β–¥–Α–≤–Ϋ–Ψ (2003βÄî2004), –Ζ –≤–Η–Ϋ–Α–Ι–¥–Β–Ϋ–Ϋ―è–Φ –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä–Η x86-64 , –Ϋ–Β –Ζ'―è–≤–Η–Μ–Η―¹―¨ 64-x ―Ä–Ψ–Ζ―Ä―è–¥–Ϋ―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Η.

–Γ―²–Α–Ϋ–¥–Α―Ä―²–Ϋ–Η–Ι –Ω'―è―²–Η–Κ―Ä–Ψ–Κ–Ψ–≤–Η–Ι –Κ–Ψ–Ϋ–≤–Β―î―Ä –≤ –Φ–Α―à–Η–Ϋ―• RISC (IF = Instruction Fetch, ID = Instruction Decode, EX = Execute, MEM = Memory access, WB = Register write back) –ö–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ–Α –Ω―Ä–Ψ–≥―Ä–Α–Φ–Α, –Ω–Ψ ―¹―É―²―•, ―î –Ω–Ψ―²–Ψ–Κ–Ψ–Φ ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι, ―â–Ψ –≤–Η–Κ–Ψ–Ϋ―É―é―²―¨―¹―è –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Ψ–Φ. –Ü–Ϋ–Ψ–¥―• ―Ü―• ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―½ –Φ–Ψ–Ε–Ϋ–Α –Ω–Β―Ä–Β–≤–Ω–Ψ―Ä―è–¥–Κ―É–≤–Α―²–Η, ―²–Α –Ψ–±'―î–¥–Ϋ–Α―²–Η –≤ –≥―Ä―É–Ω–Η, ―è–Κ―• –Ω–Ψ―²―•–Φ –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ, –±–Β–Ζ –Ζ–Φ―•–Ϋ–Η ―Ä–Β–Ζ―É–Μ―¨―²–Α―²―É ―Ä–Ψ–±–Ψ―²–Η –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η, ―â–Ψ –≤―•–¥–Ψ–Φ–Ψ ―è–Κ –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ –Ϋ–Α ―Ä―•–≤–Ϋ―• ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι. –Δ–Α–Κ–Η–Ι –Ω―•–¥―Ö―•–¥ –¥–Ψ –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Ψ―¹―²―• –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ –Ω–Β―Ä–Β–≤–Α–Ε–Α–≤ –Ζ ―¹–Β―Ä–Β–¥–Η–Ϋ–Η 80-―²–Η―Ö –¥–Ψ ―¹–Β―Ä–Β–¥–Η–Ϋ–Η 90-―²–Η―Ö.[ 19]

–Γ―É―΅–Α―¹–Ϋ―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Η –Φ–Α―é―²―¨ –±–Α–≥–Α―²–Ψ–Β―²–Α–Ω–Ϋ―• –Κ–Ψ–Ϋ–≤–Β―î―Ä–Η –Κ–Ψ–Φ–Α–Ϋ–¥ . –ö–Ψ–Ε–Β–Ϋ –Β―²–Α–Ω –Κ–Ψ–Ϋ–≤–Β―î―Ä–Α –≤―•–¥–Ω–Ψ–≤―•–¥–Α―î ―•–Ϋ―à―•–Ι –¥―•―½, ―â–Ψ –≤–Η–Κ–Ψ–Ϋ―É―î –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä. –ü―Ä–Ψ―Ü–Β―¹–Ψ―Ä ―â–Ψ –Φ–Α―î –Κ–Ψ–Ϋ–≤–Β―î―Ä –Ζ N-―¹―²―É–Ω–Β–Ϋ―è–Φ–Η, –Φ–Ψ–Ε–Β –Ψ–¥–Ϋ–Ψ―΅–Α―¹–Ϋ–Ψ –Ψ–±―Ä–Ψ–±–Μ―è―²–Η N ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι, –Κ–Ψ–Ε–Ϋ―É –Ϋ–Α ―•–Ϋ―à―•–Ι ―¹―²–Α–¥―•―½ –Ψ–±―Ä–Ψ–±–Κ–Η. –ö–Μ–Α―¹–Η―΅–Ϋ–Η–Φ –Ω―Ä–Η–Κ–Μ–Α–¥–Ψ–Φ –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α –Ζ –Κ–Ψ–Ϋ–≤–Β―î―Ä–Ψ–Φ ―î –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä–Η RISC , ―â–Ψ –Φ–Α―î –Ω'―è―²―¨ –Β―²–Α–Ω―•–≤: –Ζ–Α–≤–Α–Ϋ―²–Α–Ε–Β–Ϋ–Ϋ―è ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―½, –¥–Β–Κ–Ψ–¥―É–≤–Α–Ϋ–Ϋ―è, –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è, –¥–Ψ―¹―²―É–Ω –¥–Ψ –Ω–Α–Φ'―è―²―•, ―²–Α –Ζ–Α–Ω–Η―¹ ―Ä–Β–Ζ―É–Μ―¨―²–Α―²―É. –ü―Ä–Ψ―Ü–Β―¹–Ψ―Ä Pentium 4 –Φ–Α―î –Κ–Ψ–Ϋ–≤–Β―î―Ä –Ζ 35 –Β―²–Α–Ω–Α–Φ–Η.[ 20]

–Γ―É–Ω–Β―Ä―¹–Κ–Α–Μ―è―Ä–Ϋ–Η–Ι –Ω'―è―²–Η–Β―²–Α–Ω–Ϋ–Η–Ι –Κ–Ψ–Ϋ–≤–Β―î―Ä–Ϋ–Η–Ι –Φ―•–Κ―Ä–Ψ–Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä, ―â–Ψ –Ζ–¥–Α―²–Β–Ϋ –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η –¥–≤―• ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―½ –Ζ–Α ―Ü–Η–Κ–Μ. –£―•–Ϋ –Φ–Ψ–Ε–Β –Ζ–±–Β―Ä―•–≥–Α―²–Η –¥–≤―• ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―½ –Ϋ–Α –Κ–Ψ–Ε–Ϋ―•–Ι ―¹―²–Α–¥―•―½ –Κ–Ψ–Ϋ–≤–Β―î―Ä–Α, ―²–Α–Κ–Η–Φ ―΅–Η–Ϋ–Ψ–Φ –Ζ–Α–≥–Α–Μ–Ψ–Φ –≤–Η–Κ–Ψ–Ϋ―É―é―΅–Η –¥–Β―¹―è―²―¨ ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι –≤–Ψ–¥–Ϋ–Ψ―΅–Α―¹. –ù–Α –¥–Ψ–¥–Α―΅―É –¥–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ―É –Ϋ–Α ―Ä―•–≤–Ϋ―• ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι –¥–Β―è–Κ―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Η –Φ–Ψ–Ε―É―²―¨ –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η –±―•–Μ―¨―à –Ϋ―•–Ε –Ψ–¥–Ϋ―É ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―é –Ζ–Α ―Ä–Α–Ζ. –£–Ψ–Ϋ–Η –≤―•–¥–Ψ–Φ―• ―è–Κ ―¹―É–Ω–Β―Ä―¹–Κ–Α–Μ―è―Ä–Ϋ―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Η. –Ü–Ϋ―¹―²―Ä―É–Κ―Ü―•―½ –≥―Ä―É–Ω―É―é―²―¨―¹―è ―Ä–Α–Ζ–Ψ–Φ, ―è–Κ―â–Ψ –Φ―•–Ε –Ϋ–Η–Φ–Η –Ϋ–Β ―•―¹–Ϋ―É―î –Ζ–Α–Μ–Β–Ε–Ϋ–Ψ―¹―²―• –¥–Α–Ϋ–Η―Ö. –©–Ψ–± ―Ä–Β–Α–Μ―•–Ζ―É–≤–Α―²–Η –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ –Ϋ–Α ―Ä―•–≤–Ϋ―• ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―²―¨ –Α–Μ–≥–Ψ―Ä–Η―²–Φ–Η Scoreboarding ―²–Α Tomasulo algorithm (―è–Κ–Η–Ι –Α–Ϋ–Α–Μ–Ψ–≥―•―΅–Ϋ–Η–Ι –¥–Ψ –Ω–Ψ–Ω–Β―Ä–Β–¥–Ϋ―¨–Ψ–≥–Ψ, –Ω―Ä–Ψ―²–Β –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―î –Ω–Β―Ä–Β–Ι–Φ–Β–Ϋ―É–≤–Α–Ϋ–Ϋ―è ―Ä–Β–≥―•―¹―²―Ä―•–≤ ).

–ü–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ –¥–Α–Ϋ–Η―Ö βÄî ―Ü–Β –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ –≤–Μ–Α―¹―²–Η–≤–Η–Ι ―Ü–Η–Κ–Μ–Α–Φ –Ω―Ä–Ψ–≥―Ä–Α–Φ , ―è–Κ―• ―³–Ψ–Κ―É―¹―É―é―²―¨―¹―è –Ϋ–Α –¥–Ψ―¹―²–Α–≤―Ü―• –¥–Α–Ϋ–Η―Ö ―Ä―•–Ζ–Ϋ–Η–Φ –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ–Η–Φ –≤―É–Ζ–Μ–Α–Φ –¥–Μ―è –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ―½ –Ψ–±―Ä–Ψ–±–Κ–Η. "–†–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é–≤–Α–Ϋ–Ϋ―è ―Ü–Η–Κ–Μ―•–≤ ―΅–Α―¹―²–Ψ –Ω―Ä–Η–≤–Ψ–¥–Η―²―¨ –¥–Ψ –Ω–Ψ–¥―•–±–Ϋ–Η―Ö (–Ϋ–Β –Ψ–±–Ψ–≤'―è–Ζ–Κ–Ψ–≤–Ψ ―•–¥–Β–Ϋ―²–Η―΅–Ϋ–Η―Ö) –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Ψ―¹―²–Β–Ι –Ψ–Ω–Β―Ä–Α―Ü―•–Ι, ―΅–Η –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è ―³―É–Ϋ–Κ―Ü―•–Ι –Ϋ–Α–¥ –Β–Μ–Β–Φ–Β–Ϋ―²–Α–Φ–Η –≤–Β–Μ–Η–Κ–Η―Ö ―¹―²―Ä―É–Κ―²―É―Ä –¥–Α–Ϋ–Η―Ö.[ 21]

–Π–Η–Κ–Μ―•―΅–Ϋ–Α –Ζ–Α–Μ–Β–Ε–Ϋ―•―¹―²―¨ βÄî –Ζ–Α–Μ–Β–Ε–Ϋ―•―¹―²―¨ ―•―²–Β―Ä–Α―Ü―•―½ ―Ü–Η–Κ–Μ―É, –≤―•–¥ ―Ä–Β–Ζ―É–Μ―¨―²–Α―²―•–≤ –Ω–Ψ–Ω–Β―Ä–Β–¥–Ϋ―¨–Ψ―½, ―΅–Η –Κ―•–Μ―¨–Κ–Ψ―Ö –Ω–Ψ–Ω–Β―Ä–Β–¥–Ϋ―•―Ö ―•―²–Β―Ä–Α―Ü―•–Ι. –Π–Η–Κ–Μ―•―΅–Ϋ―• –Ζ–Α–Μ–Β–Ε–Ϋ–Ψ―¹―²―• –Ω–Β―Ä–Β―à–Κ–Ψ–¥–Ε–Α―é―²―¨ ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é–≤–Α–Ϋ–Ϋ―é ―Ü–Η–Κ–Μ―•–≤. –†–Ψ–Ζ–≥–Μ―è–Ϋ–Β–Φ–Ψ –Ω―¹–Β–≤–¥–Ψ–Κ–Ψ–¥ , ―â–Ψ –Ψ–±―΅–Η―¹–Μ―é―î –Κ―•–Μ―¨–Κ–Α –Ω–Β―Ä―à–Η―Ö ―΅–Η―¹–Β–Μ ―³―•–±–Ψ–Ϋ–Α―΅―΅―• :

1: PREV1 := 0

2: PREV2 := 1

4: do:

5: CUR := PREV1 + PREV2

6: PREV1 := PREV2

7: PREV2 := CUR

8: while (CUR < 10)

–Δ–Α–Κ–Η–Ι ―Ü–Η–Κ–Μ –Ϋ–Β –Φ–Ψ–Ε–Β –±―É―²–Η ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ–Β–Ϋ–Η–Ι, –±–Ψ CUR –Ζ–Α–Μ–Β–Ε–Η―²―¨ –≤―•–¥ ―¹–Β–±–Β (PREV2), ―²–Α PREV1, ―è–Κ―• –Ψ–±―΅–Η―¹–Μ―é―é―²―¨―¹―è –≤ –Κ–Ψ–Ε–Ϋ―•–Ι ―•―²–Β―Ä–Α―Ü―•―½. –Δ–Ψ–Φ―É, –Κ–Ψ–Ε–Ϋ–Α ―•―²–Β―Ä–Α―Ü―•―è –Ζ–Α–Μ–Β–Ε–Η―²―¨ –≤―•–¥ ―Ä–Β–Ζ―É–Μ―¨―²–Α―²―•–≤ –Ω–Ψ–Ω–Β―Ä–Β–¥–Ϋ―¨–Ψ―½, –≤–Ψ–Ϋ–Η –Ϋ–Β –Φ–Ψ–Ε―É―²―¨ –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η―¹―¨ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ. –ö–Ψ–Μ–Η ―Ä–Ψ–Ζ–Φ―•―Ä –Ζ–Α–¥–Α―΅―• ―¹―²–Α―î –±―•–Μ―¨―à–Η–Φ, –Κ―•–Μ―¨–Κ―•―¹―²―¨ –¥–Ψ―¹―²―É–Ω–Ϋ–Η―Ö –¥–Μ―è ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é–≤–Α–Ϋ–Ϋ―è –¥–Α–Ϋ–Η―Ö –Ζ–Α–Ζ–≤–Η―΅–Α–Ι ―²–Β–Ε –Ζ―Ä–Ψ―¹―²–Α―î.[ 22]

–ü–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ –Ζ–Α–¥–Α―΅ βÄî ―Ö–Α―Ä–Α–Κ―²–Β―Ä–Η―¹―²–Η–Κ–Α –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ―½ –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η, ―è–Κ–Α –Ω–Ψ–Μ―è–≥–Α―î –≤ ―²–Ψ–Φ―É, ―â–Ψ ¬Ϊ―Ü―•–Μ–Κ–Ψ–Φ ―Ä―•–Ζ–Ϋ―• –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è –Φ–Ψ–Ε―É―²―¨ –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η―¹―¨ –Ϋ–Α–¥ –Ψ–¥–Ϋ–Η–Φ–Η, ―΅–Η ―Ä―•–Ζ–Ϋ–Η–Φ–Η –¥–Α–Ϋ–Η–Φ–Η¬Μ.[ 21] [ 22]

–û―¹–Ϋ–Ψ–≤–Ϋ–Ψ―é –Ω–Α–Φ'―è―²―²―é –≤ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ–Φ―É –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―• ―î ―è–Κ ―¹–Ω―•–Μ―¨–Ϋ–Α –Ω–Α–Φ'―è―²―¨ (―Ä–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Α –Φ―•–Ε –≤―¹―•–Φ–Α –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ–Η–Φ–Η –Β–Μ–Β–Φ–Β–Ϋ―²–Α–Φ–Η –≤ –Ψ–¥–Ϋ–Ψ–Φ―É –Α–¥―Ä–Β―¹–Ϋ–Ψ–Φ―É –Ω―Ä–Ψ―¹―²–Ψ―Ä―• ), ―΅–Η ―Ä–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Α –Ω–Α–Φ'―è―²―¨ (–≤ ―è–Κ―•–Ι –Κ–Ψ–Ε–Β–Ϋ –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ–Η–Ι –Β–Μ–Β–Φ–Β–Ϋ―² –Φ–Α―î ―¹–≤―•–Ι –≤–Μ–Α―¹–Ϋ–Η–Ι –Μ–Ψ–Κ–Α–Μ―¨–Ϋ–Η–Ι –Α–¥―Ä–Β―¹–Ϋ–Η–Ι –Ω―Ä–Ψ―¹―²―•―Ä).[ 23] –†–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Α ―¹–Ω―•–Μ―¨–Ϋ–Α –Ω–Α–Φ'―è―²―¨ ―²–Α –≤―•―Ä―²―É–Α–Μ―•–Ζ–Α―Ü―•―è –Ω–Α–Φ'―è―²―• –Κ–Ψ–Φ–±―•–Ϋ―É―é―²―¨ –Ψ–±–Η–¥–≤–Α –Ω―•–¥―Ö–Ψ–¥–Η, –¥–Β –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ–Η–Ι –Β–Μ–Β–Φ–Β–Ϋ―² –Φ–Α―î ―¹–≤–Ψ―é –≤–Μ–Α―¹–Ϋ―É –Μ–Ψ–Κ–Α–Μ―¨–Ϋ―É –Ω–Α–Φ'―è―²―¨, ―²–Α –¥–Ψ―¹―²―É–Ω –¥–Ψ –Ω–Α–Φ'―è―²―• ―•–Ϋ―à–Η―Ö –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤. –î–Ψ―¹―²―É–Ω –¥–Ψ –Μ–Ψ–Κ–Α–Μ―¨–Ϋ–Ψ―½ –Ω–Α–Φ'―è―²―• –Ζ–Α–Ζ–≤–Η―΅–Α–Ι ―à–≤–Η–¥―à–Η–Ι –Ϋ―•–Ε –¥–Ψ―¹―²―É–Ω –¥–Ψ –Ϋ–Β–Μ–Ψ–Κ–Α–Μ―¨–Ϋ–Ψ―½.

–Γ―²―Ä―É–Κ―²―É―Ä–Α –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä–Η Non-Uniform Memory Access (NUMA). –ü―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Η –≤ –Ψ–¥–Ϋ―•–Ι –¥–Η―Ä–Β–Κ―²–Ψ―Ä―•―½ –Φ–Ψ–Ε―É―²―¨ –Ψ―²―Ä–Η–Φ–Α―²–Η –¥–Ψ―¹―²―É–Ω –¥–Ψ –Ω–Α–Φ'―è―²―• ―²―•―î―½ –¥–Η―Ä–Β–Κ―²–Ψ―Ä―•―½ –Ζ–Α –Φ–Β–Ϋ―à–Η–Ι ―΅–Α―¹ –Ϋ―•–Ε –≤ ―•–Ϋ―à–Η―Ö –¥–Η―Ä–Β–Κ―²–Ψ―Ä―•―è―Ö. –ö–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ―• –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä–Η –≤ ―è–Κ–Η―Ö –¥–Ψ―¹―²―É–Ω –¥–Ψ –Κ–Ψ–Ε–Ϋ–Ψ–≥–Ψ –Β–Μ–Β–Φ–Β–Ϋ―²―É –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Ψ―½ –Ω–Α–Φ'―è―²―• –Ζ–Α–Ι–Φ–Α―î –Ψ–¥–Ϋ–Α–Κ–Ψ–≤–Η–Ι ―΅–Α―¹ ―²–Α ―²―Ä–Α―³―•–Κ –Ϋ–Α–Ζ–Η–≤–Α―é―²―¨―¹―è ―¹–Η―¹―²–Β–Φ–Α–Φ–Η –Ζ –Ψ–¥–Ϋ–Ψ―Ä―•–¥–Ϋ–Η–Φ –¥–Ψ―¹―²―É–Ω–Ψ–Φ –¥–Ψ –Ω–Α–Φ'―è―²―• Uniform Memory Access (UMA). –½–Α–Ζ–≤–Η―΅–Α–Ι, ―Ü–Β –¥–Ψ―¹―è–≥–Α―î―²―¨―¹―è ―²―•–Μ―¨–Κ–Η –Ζ ―¹–Ω―•–Μ―¨–Ϋ–Ψ―é –Ω–Α–Φ'―è―²―²―é, –≤ ―è–Κ―•–Ι –Ω–Α–Φ'―è―²―¨ –Ϋ–Β ―î ―³―•–Ζ–Η―΅–Ϋ–Ψ ―Ä–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Α. –Γ–Η―¹―²–Β–Φ–Α ―â–Ψ –Ϋ–Β –≤–Ψ–Μ–Ψ–¥―•―î ―²–Α–Κ–Ψ―é –≤–Μ–Α―¹―²–Η–≤―•―¹―²―é –Ϋ–Α–Ζ–Η–≤–Α―î―²―¨―¹―è –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä–Ψ―é –Ζ –Ϋ–Β–Ψ–¥–Ϋ–Ψ―Ä―•–¥–Ϋ–Η–Φ –¥–Ψ―¹―²―É–Ω–Ψ–Φ –¥–Ψ –Ω–Α–Φ'―è―²―• (Non-Uniform Memory Access (NUMA)). –Γ–Η―¹―²–Β–Φ–Η –Ζ ―Ä–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Ψ―é –Ω–Α–Φ'―è―²―²―é –Φ–Α―é―²―¨ –Ϋ–Β–Ψ–¥–Ϋ–Ψ―Ä―•–¥–Ϋ–Η–Ι –¥–Ψ―¹―²―É–Ω –¥–Ψ –Ω–Α–Φ'―è―²―•.

–ö–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ―• ―¹–Η―¹―²–Β–Φ–Η –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―²―¨ –Φ–Α–Μ–Β–Ϋ―¨–Κ―•, ―à–≤–Η–¥–Κ―•, –Κ–Β―à-–Ω–Α–Φ'―è―²―•, ―â–Ψ ―Ä–Ψ–Ζ–Φ―•―â―É―é―²―¨―¹―è –±–Μ–Η–Ζ―¨–Κ–Ψ –¥–Ψ –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α, ―²–Α –Ζ–±–Β―Ä―•–≥–Α―é―²―¨ ―²–Η–Φ―΅–Α―¹–Ψ–≤―• –Κ–Ψ–Ω―•―½ –Ζ–Φ―•–Ϋ–Ϋ–Η―Ö –Ω–Α–Φ'―è―²―• (―è–Κ ―É ―³―•–Ζ–Η―΅–Ϋ–Ψ–Φ―É, ―²–Α–Κ ―• –Μ–Ψ–≥―•―΅–Ϋ–Ψ–Φ―É ―¹–Φ–Η―¹–Μ–Α―Ö). –ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Η –Φ–Α―é―²―¨ –Ω―Ä–Ψ–±–Μ–Β–Φ–Η –Ζ –Κ–Β―à–Α–Φ–Η, ―â–Ψ –Φ–Ψ–Ε―É―²―¨ –Ζ–±–Β―Ä―•–≥–Α―²–Η –Ψ–¥–Ϋ―• ―• ―²―• –Ε –Ζ–Ϋ–Α―΅–Β–Ϋ–Ϋ―è –≤ –Κ―•–Μ―¨–Κ–Ψ―Ö –Φ―•―¹―Ü―è―Ö, ―â–Ψ ―¹―²–≤–Ψ―Ä―é―î –Φ–Ψ–Ε–Μ–Η–≤–Ψ―¹―²―• –¥–Μ―è –Ϋ–Β–Ω―Ä–Α–≤–Η–Μ―¨–Ϋ–Ψ–≥–Ψ –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨. –Δ–Α–Κ―• –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Η –≤–Η–Φ–Α–≥–Α―é―²―¨ ―¹–Η―¹―²–Β–Φ―É –Κ–Ψ–≥–Β―Ä–Β–Ϋ―Ü―•―½ –Κ–Β―à―É , ―è–Κ–Α ―¹–Μ―•–¥–Κ―É―î –Ζ–Α –Κ–Β―à–Ψ–≤–Α–Ϋ–Η–Φ–Η –Ζ–Φ―•–Ϋ–Ϋ–Η–Φ–Η ―²–Α –≤―΅–Α―¹–Ϋ–Ψ –Ψ―΅–Η―â―É―î ―½―Ö, –Ζ–Α–±–Β–Ζ–Ω–Β―΅―É―é―΅–Η –Κ–Ψ―Ä–Β–Κ―²–Ϋ–Β –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η. –ü―Ä–Ψ–Ϋ―é―Ö―É–≤–Α–Ϋ–Ϋ―è ―à–Η–Ϋ–Η [en] [ 23]

–ö–Ψ–Φ―É–Ϋ―•–Κ–Α―Ü―•―è –Φ―•–Ε –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α–Φ–Η, ―²–Α –Φ―•–Ε –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α–Φ–Η ―²–Α –Ω–Α–Φ'―è―²―²―é –Φ–Ψ–Ε–Β –±―É―²–Η ―Ä–Β–Α–Μ―•–Ζ–Ψ–≤–Α–Ϋ–Α –Α–Ω–Α―Ä–Α―²–Ϋ–Ψ –Κ―•–Μ―¨–Κ–Ψ–Φ–Α ―¹–Ω–Ψ―¹–Ψ–±–Α–Φ–Η, –≤–Κ–Μ―é―΅–Α―é―΅–Η ―¹–Ω―•–Μ―¨–Ϋ―É (–Φ―É–Μ―¨―²–Η–Ω–Ψ―Ä―²–Ψ–≤―É ―΅–Η –€―É–Μ―¨―²–Η–Ω–Μ–Β–Κ―¹–Ϋ―É ) –Ω–Α–Φ'―è―²―¨, –Φ–Α―²―Ä–Η―΅–Ϋ–Η–Ι –Ω–Β―Ä–Β–Φ–Η–Κ–Α―΅ , ―¹–Ω―•–Μ―¨–Ϋ―É ―à–Η–Ϋ―É ―΅–Η –Φ–Β―Ä–Β–Ε–Α –Ψ–¥–Ϋ―•―î―½ –Ζ ―²–Η―¹―è―΅ ―²–Ψ–Ω–Ψ–Μ–Ψ–≥―•–Ι , –≤–Κ–Μ―é―΅–Α―é―΅–Η –Ζ―•―Ä–Κ―É, –Κ―•–Μ―¨―Ü–Β, –¥–Β―Ä–Β–≤–Ψ, –≥―•–Ω–Β―Ä–Κ―É–± , –Ε–Η―Ä–Ϋ–Η–Ι –≥―•–Ω–Β―Ä–Κ―É–± (–≥―•–Ω–Β―Ä–Κ―É–± –Ζ –±―•–Μ―¨―à –Ϋ―•–Ε –Ψ–¥–Ϋ–Η–Φ –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Ψ–Φ ―É –≤–Β―Ä―à–Η–Ϋ―•), ―΅–Η n-–≤–Η–Φ―•―Ä–Ϋ―É ―¹―•―²–Κ―É.

–ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Η ―â–Ψ –±–Α–Ζ―É―é―²―¨―¹―è –Ϋ–Α –Ζ–≤'―è–Ζ–Α–Ϋ–Η―Ö –Φ–Β―Ä–Β–Ε–Α―Ö –Φ–Α―é―²―¨ –Φ–Α―²–Η –Ω–Β–≤–Ϋ―É –Φ–Α―Ä―à―Ä―É―²–Η–Ζ–Α―Ü―•―é ―â–Ψ–± –Ζ–Α–±–Β–Ζ–Ω–Β―΅–Η―²–Η –Ω–Β―Ä–Β–¥–Α–≤–Α–Ϋ–Ϋ―è –Ω–Ψ–≤―•–¥–Ψ–Φ–Μ–Β–Ϋ―¨ –Φ―•–Ε –Β–Μ–Β–Φ–Β–Ϋ―²–Α–Φ–Η ―â–Ψ –Ϋ–Β ―î –Ζ–≤'―è–Ζ–Α–Ϋ―• –Ϋ–Α–Ω―Ä―è–Φ―É. –€–Β–¥―•–Α ―â–Ψ –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―î―²―¨―¹―è –¥–Μ―è –Ζ–≤'―è–Ζ–Κ―É –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤ ―΅–Α―¹―²–Ψ –±―É–≤–Α―î ―•―î―Ä–Α―Ä―Ö―•―΅–Ϋ–Η–Φ ―É –≤–Β–Μ–Η–Κ–Η―Ö –±–Α–≥–Α―²–Ψ–Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Ϋ–Η―Ö –Φ–Α―à–Η–Ϋ–Α―Ö.

–ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Η –Φ–Ψ–Ε–Ϋ–Α –≥―Ä―É–±–Ψ –Κ–Μ–Α―¹–Η―³―•–Κ―É–≤–Α―²–Η –Ζ–Α ―Ä―•–≤–Ϋ–Β–Φ, –Ϋ–Α ―è–Κ–Ψ–Φ―É –Α–Ω–Α―Ä–Α―²–Ϋ–Β –Ζ–Α–±–Β–Ζ–Ω–Β―΅–Β–Ϋ–Ϋ―è –Ω―•–¥―²―Ä–Η–Φ―É―î –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ. –Δ–Α–Κ–Α –Κ–Μ–Α―¹–Η―³―•–Κ–Α―Ü―•―è –Φ–Α–Ι–Ε–Β –Α–Ϋ–Α–Μ–Ψ–≥―•―΅–Ϋ–Α –≤―•–¥―¹―²–Α–Ϋ―• –Φ―•–Ε –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Η–Φ–Η –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ–Η–Φ–Η –Β–Μ–Β–Φ–Β–Ϋ―²–Α–Φ–Η.

–ë–Α–≥–Α―²–Ψ―è–¥–Β―Ä–Ϋ–Η–Ι –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä βÄî ―Ü–Β –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä , ―â–Ψ –Φ―•―¹―²–Η―²―¨ –Κ―•–Μ―¨–Κ–Α ―è–¥–Β―Ä. –Π―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Η –≤―•–¥―Ä―•–Ζ–Ϋ―è―é―²―¨―¹―è –≤―•–¥ ―¹―É–Ω–Β―Ä―¹–Κ–Α–Μ―è―Ä–Ϋ–Η―Ö –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤, ―è–Κ―• –Φ–Ψ–Ε―É―²―¨ –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η –Κ―•–Μ―¨–Κ–Α ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι –Ζ–Α ―²–Α–Κ―² –Ζ –Ψ–¥–Ϋ–Ψ–≥–Ψ –Ω–Ψ―²–Ψ–Κ―É ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι (–Ϋ–Η―²–Κ–Η ); –Ϋ–Α –≤―•–¥–Φ―•–Ϋ―É –≤―•–¥ –±–Α–≥–Α―²–Ψ―è–¥–Β―Ä–Ϋ–Η―Ö, ―â–Ψ –Φ–Ψ–Ε―É―²―¨ –Ζ–Α ―²–Α–Κ―² –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η –Κ―•–Μ―¨–Κ–Α ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι –Ζ ―Ä―•–Ζ–Ϋ–Η―Ö –Ϋ–Η―²–Ψ–Κ. –ö–Ψ–Ε–Ϋ–Β ―è–¥―Ä–Ψ –±–Α–≥–Α―²–Ψ―è–¥–Β―Ä–Ϋ–Ψ–≥–Ψ –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α –Ω–Ψ―²–Β–Ϋ―Ü―•–Ι–Ϋ–Ψ –Φ–Ψ–Ε–Β –±―É―²–Η ―¹―É–Ω–Β―Ä―¹–Κ–Α–Μ―è―Ä–Ϋ–Η–Φ, ―²–Ψ–±―²–Ψ –≤–Η–Κ–Ψ–Ϋ―É–≤–Α―²–Η –Ω–Ψ –Κ―•–Μ―¨–Κ–Α ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•–Ι –Ζ –Ψ–¥–Ϋ–Ψ―½ –Ϋ–Η―²–Κ–Η.

–Γ–Η–Ϋ―Ö―Ä–Ψ–Ϋ–Ϋ–Α –±–Α–≥–Α―²–Ψ–Ϋ–Η―²–Β–≤―•―¹―²―¨ (–Ϋ–Α–Ι–≤―•–¥–Ψ–Φ―•―à–Ψ―é –Ζ ―è–Κ–Η―Ö ―î ―²–Β―Ö–Ϋ–Ψ–Μ–Ψ–≥―•―è HyperThreading –≤―•–¥ Intel ) –±―É–Μ–Α ―Ä–Α–Ϋ–Ϋ―¨–Ψ―é ―³–Ψ―Ä–Φ–Ψ―é –Ω―¹–Β–≤–¥–Ψ-–±–Α–≥–Α―²–Ψ―è–¥–Β―Ä–Ϋ–Ψ―¹―²―•. –ü―Ä–Ψ―Ü–Β―¹–Ψ―Ä, ―â–Ψ –Ζ–¥–Α―²–Β–Ϋ –¥–Ψ ―¹–Η–Ϋ―Ö―Ä–Ψ–Ϋ–Ϋ–Ψ―½ –±–Α–≥–Α―²–Ψ–Ϋ–Η―²–Β–≤–Ψ―¹―²―• –Φ–Α―î –Μ–Η―à –Ψ–¥–Ϋ–Β ―è–¥―Ä–Ψ, –Α–Μ–Β –Ω―Ä–Η –Ω―Ä–Ψ―¹―²–Ψ―è―Ö ―è–¥―Ä–Α (–Ϋ–Α–Ω―Ä–Η–Κ–Μ–Α–¥ –Ω―•–¥ ―΅–Α―¹ –Ψ―΅―•–Κ―É–≤–Α–Ϋ–Ϋ―è –Ω―•–¥–≤–Α–Ϋ―²–Α–Ε–Β–Ϋ–Ϋ―è –¥–Α–Ϋ–Η―Ö –≤ ―¹―²–Β–Κ), –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―î ―Ü–Β ―è–¥―Ä–Ψ –¥–Μ―è ―Ä–Ψ–±–Ψ―²–Η –Ζ ―•–Ϋ―à–Ψ―é –Ϋ–Η―²―²―é. –€―•–Κ―Ä–Ψ–Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä Cell –≤―•–¥ IBM , ―â–Ψ ―¹―²–≤–Ψ―Ä–Β–Ϋ–Η–Ι –¥–Μ―è –≤–Η–Κ–Ψ―Ä–Η―¹―²–Α–Ϋ–Ϋ―è –≤ –Κ–Ψ–Ϋ―¹–Ψ–Μ―è―Ö Sony PlayStation 3 ―î ―•–Ϋ―à–Η–Φ –Ω―Ä–Η–Κ–Μ–Α–¥–Ψ–Φ –±–Α–≥–Α―²–Ψ―è–¥–Β―Ä–Ϋ–Ψ–≥–Ψ –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α.

–Γ–Η–Φ–Β―²―Ä–Η―΅–Ϋ–Η–Ι –Φ―É–Μ―¨―²–Η–Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä (SMP) ―Ü–Β –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ–Α ―¹–Η―¹―²–Β–Φ–Α –Ζ –±–Α–≥–Α―²―¨–Φ–Α ―•–¥–Β–Ϋ―²–Η―΅–Ϋ–Η–Φ–Η –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α–Φ–Η , ―â–Ψ –Ω–Ψ–¥―•–Μ―è―é―²―¨ –Ω–Α–Φ'―è―²―¨ , ―²–Α –Ζ'―î–¥–Ϋ―É―é―²―¨―¹―è ―΅–Β―Ä–Β–Ζ ―à–Η–Ϋ―É .[ 24] –®–Η–Ϋ–Ϋ–Α ―¹―É–Ω–Β―Ä–Β―΅–Κ–Α [en] –Α–Ϋ–≥–Μ. bus contention ) –Ω–Β―Ä–Β―à–Κ–Ψ–¥–Ε–Α―î –Φ–Α―¹―à―²–Α–±―É–≤–Α–Ϋ–Ϋ―é ―à–Η–Ϋ–Ϋ–Η―Ö –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä. –£ ―Ä–Β–Ζ―É–Μ―¨―²–Α―²―•, SMP –Ζ–Α–Ζ–≤–Η―΅–Α–Ι –Ϋ–Β –Φ―•―¹―²–Η―²―¨ –±―•–Μ―¨―à–Β 32-x –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤.[ 25] [ 24]

–†–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Η–Ι –Κ–Ψ–Φ–Ω'―é―²–Β―Ä (―²–Α–Κ–Ψ–Ε –≤―•–¥–Ψ–Φ–Η–Ι ―è–Κ –Φ―É–Μ―¨―²–Η–Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä –Ζ ―Ä–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Ψ―é –Ω–Α–Φ'―è―²―²―é) ―Ü–Β –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ–Α ―¹–Η―¹―²–Β–Φ–Α –Ζ ―Ä–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Ψ―é –Ω–Α–Φ'―è―²―²―é, ―É ―è–Κ―•–Ι –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ―• –Β–Μ–Β–Φ–Β–Ϋ―²–Η –Ζ'―î–¥–Ϋ–Α–Ϋ―• –Φ–Β―Ä–Β–Ε–Β―é. –†–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ―• –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Η ―΅―É–¥–Ψ–≤–Ψ –Φ–Α―¹―à―²–Α–±―É―é―²―¨―¹―è.

–ö–Μ–Α―¹―²–Β―Ä Beowulf –ö–Μ–Α―¹―²–Β―Ä βÄî ―Ü–Β –≥―Ä―É–Ω–Α ―¹–Μ–Α–±–Ψ –Ζ–≤'―è–Ζ–Α–Ϋ–Η―Ö –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤, ―â–Ψ ―²―•―¹–Ϋ–Ψ ―¹–Ω―•–≤–Ω―Ä–Α―Ü―é―é―²―¨, ―²–Α–Κ ―â–Ψ –≤ –Ω–Β–≤–Ϋ–Ψ―é –Φ―•―Ä–Ψ―é, –≤–Ψ–Ϋ–Η –Φ–Ψ–Ε―É―²―¨ ―Ä–Ψ–Ζ–≥–Μ―è–¥–Α―²–Η―¹―¨ ―è–Κ –Ψ–¥–Η–Ϋ –Κ–Ψ–Φ–Ω'―é―²–Β―Ä.[ 26] –±–Α–Μ–Α–Ϋ―¹―É–≤–Α–Ϋ–Ϋ―è –Ϋ–Α–≤–Α–Ϋ―²–Α–Ε–Β–Ϋ–Ϋ―è . –ù–Α–Ι–Ω–Ψ―à–Η―Ä–Β–Ϋ―•―à–Η–Φ ―²–Η–Ω–Ψ–Φ –Κ–Μ–Α―¹―²–Β―Ä–Α ―î –Κ–Μ–Α―¹―²–Β―Ä Beowulf , ―è–Κ–Η–Ι ―î –Κ–Μ–Α―¹―²–Β―Ä–Ψ–Φ, ―Ä–Β–Α–Μ―•–Ζ–Ψ–≤–Α–Ϋ–Η–Φ –Ϋ–Α –±–Α–≥–Α―²―¨–Ψ―Ö ―•–¥–Β–Ϋ―²–Η―΅–Ϋ–Η―Ö ―³–Α–±―Ä–Η―΅–Ϋ–Η―Ö –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Α―Ö, –Ζ'―î–¥–Ϋ–Α–Ϋ–Η―Ö –≤ –Μ–Ψ–Κ–Α–Μ―¨–Ϋ―É –Φ–Β―Ä–Β–Ε―É TCP/IP Ethernet .[ 27] –Δ–Ψ–Φ–Α―¹ –Γ―²–Β―Ä–Μ―•–Ϋ–≥ ―²–Α –î–Ψ–Ϋ–Α–Μ―¨–¥ –ë–Β–Κ–Κ–Β―Ä . –ë―•–Μ―¨―à―•―¹―²―¨ ―¹―É–Ω–Β―Ä–Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤ –Ζ―• ―¹–Ω–Η―¹–Κ―É TOP500 ―î –Κ–Μ–Α―¹―²–Β―Ä–Α–Φ–Η.[ 28]

–€–Α―¹–Η–≤–Ϋ–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η–Ι –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä (MPP) ―Ü–Β –Ψ–¥–Η–Ϋ –Κ–Ψ–Φ–Ω'―é―²–Β―Ä –Ζ –±–Α–≥–Α―²―¨–Φ–Α –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α–Φ–Η –Ζ'―î–¥–Ϋ–Α–Ϋ–Η–Φ–Η –≤ –Φ–Β―Ä–Β–Ε―É. MPP –Φ–Α―é―²―¨ –±–Α–≥–Α―²–Ψ ―¹–Ω―•–Μ―¨–Ϋ–Ψ–≥–Ψ –Ζ –Κ–Μ–Α―¹―²–Β―Ä–Α–Φ–Η, ―²–Α MPP –Φ–Α―é―²―¨ ―¹–Ω–Β―Ü―•–Α–Μ―•–Ζ–Ψ–≤–Α–Ϋ―• –Ζ'―î–¥–Ϋ―É–≤–Α–Μ―¨–Ϋ―• –Φ–Β―Ä–Β–Ε―• (―²–Ψ–¥―• ―è–Κ –Κ–Μ–Α―¹―²–Β―Ä–Η –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―²―¨ ―¹―²–Ψ―Ä–Ψ–Ϋ–Ϋ―î –Ψ–±–Μ–Α–¥–Ϋ–Α–Ϋ–Ϋ―è –¥–Μ―è –Φ–Β―Ä–Β–Ε―•). MPP ―²–Α–Κ–Ψ–Ε –≤ –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Ψ–Φ―É –±―•–Μ―¨―à―• –Ϋ―•–Ε –Κ–Μ–Α―¹―²–Β―Ä–Η, –Ζ–Α–Ζ–≤–Η―΅–Α–Ι –Φ–Α―é―²―¨ ¬Ϊ–Ϋ–Α–±–Α–≥–Α―²–Ψ –±―•–Μ―¨―à–Β –Ϋ―•–Ε 100 –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤¬Μ.[ 29] [ 30]

–®–Α―³–Κ–Α Blue Gene /L, ―â–Ψ –Φ–Α―î ―Ä–Β–Ι―²–Η–Ϋ–≥ ―΅–Β―²–≤–Β―Ä―²–Ψ–≥–Ψ –Ϋ–Α–Ι―à–≤–Η–¥―à–Ψ–≥–Ψ ―¹―É–Ω–Β―Ä–Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Α ―É ―¹–≤―•―²―•, –Ζ–≥―•–¥–Ϋ–Ψ –Ζ ―Ä–Β–Ι―²–Η–Ϋ–≥–Ψ–Φ TOP500 11/2008. Blue Gene/L –Φ–Α―¹–Η–≤–Ϋ–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η–Ι –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä. Blue Gene /L, –Φ–Α―î ―Ä–Β–Ι―²–Η–Ϋ–≥ ―΅–Β―²–≤–Β―Ä―²–Ψ–≥–Ψ –Ϋ–Α–Ι―à–≤–Η–¥―à–Ψ–≥–Ψ ―¹―É–Ω–Β―Ä–Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Α ―É ―¹–≤―•―²―•, –Ζ–≥―•–¥–Ϋ–Ψ –Ζ ―Ä–Β–Ι―²–Η–Ϋ–≥–Ψ–Φ TOP500 11/2008. Blue Gene/L –Φ–Α―¹–Η–≤–Ϋ–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η–Ι –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä.

–û–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è “ê―Ä―•–¥ βÄî –Ϋ–Α–Ι–±―•–Μ―¨―à ―Ä–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Α ―³–Ψ―Ä–Φ–Α –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨. –£–Ψ–Ϋ–Α –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―î –¥–Μ―è ―Ä–Ψ–Ζ–≤'―è–Ζ–Α–Ϋ–Ϋ―è –Ζ–Α–¥–Α―΅―• –Ζ–≤'―è–Ζ–Α–Ϋ―• –Φ–Β―Ä–Β–Ε–Β―é –Ü–Ϋ―²–Β―Ä–Ϋ–Β―² –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Η. –ß–Β―Ä–Β–Ζ –Ϋ–Η–Ζ―¨–Κ―É ―à–≤–Η–¥–Κ―•―¹―²―¨ –Ω–Β―Ä–Β–¥–Α―΅―• –¥–Α–Ϋ–Η―Ö, ―²–Α –≤―•–¥–Ϋ–Ψ―¹–Ϋ–Ψ –≤–Β–Μ–Η–Κ–Η–Ι ―΅–Α―¹ –¥–Ψ―¹―²―É–Ω―É –¥–Ψ –¥–Α–Ϋ–Η―Ö –≤ –Ü–Ϋ―²–Β―Ä–Ϋ–Β―², “ë―Ä―•–¥ –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ–≤–Ψ–¥―è―²―¨ ―²―•–Μ―¨–Κ–Η –¥–Μ―è –Ω―Ä–Η–≥–Ψ–Μ–Ψ–Φ―à–Μ–Η–≤–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Ζ–Α–¥–Α―΅. –Γ―²–≤–Ψ―Ä–Β–Ϋ–Α –±–Α–≥–Α―²–Ψ –Ζ–Α―¹―²–Ψ―¹―É–≤–Α–Ϋ―¨ “ë―Ä―•–¥ ―¹–Η―¹―²–Β–Φ–Α–Φ , –Ϋ–Α–Ι–≤―•–¥–Ψ–Φ―•―à–Η–Φ–Η –Ζ ―è–Κ–Η―Ö ―î SETI@home ―²–Α Folding@Home [ 31]

–ë―•–Μ―¨―à―•―¹―²―¨ –Ω―Ä–Ψ–≥―Ä–Α–Φ “ë―Ä―•–¥ –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―²―¨ –Ω―Ä–Ψ–Φ―•–Ε–Ϋ–Β –Ω―Ä–Ψ–≥―Ä–Α–Φ–Ϋ–Β –Ζ–Α–±–Β–Ζ–Ω–Β―΅–Β–Ϋ–Ϋ―è, ―â–Ψ ―¹–Μ―É–≥―É―î ―•–Ϋ―²–Β―Ä―³–Β–Ι―¹–Ψ–Φ –Φ―•–Ε –Ψ–Ω–Β―Ä–Α―Ü―•–Ι–Ϋ–Ψ―é ―¹–Η―¹―²–Β–Φ–Ψ―é, ―²–Α –Ω―Ä–Ψ–≥―Ä–Α–Φ–Ψ―é, ―²–Α –Κ–Β―Ä―É―î ―Ä–Β―¹―É―Ä―¹–Α–Φ–Η –Φ–Β―Ä–Β–Ε―•, ―• ―¹―²–Α–Ϋ–¥–Α―Ä―²–Η–Ζ―É―î ―•–Ϋ―²–Β―Ä―³–Β–Ι―¹. –ù–Α–Ι–Ω–Ψ―à–Η―Ä–Β–Ϋ―•―à–Η–Φ –Ω―Ä–Ψ–≥―Ä–Α–Φ–Ϋ–Η–Φ –Ζ–Α–±–Β–Ζ–Ω–Β―΅–Β–Ϋ–Ϋ―è–Φ ―Ü―¨–Ψ–≥–Ψ ―²–Η–Ω―É ―î Berkeley Open Infrastructure for Network Computing (BOINC). –ß–Α―¹―²–Ψ –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η “ë―Ä―•–¥ –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ –Κ–Ψ―Ä–Η―¹―²―É―é―²―¨―¹―è ¬Ϊ–Ζ–Α–Ω–Α―¹–Ϋ–Η–Φ–Η ―Ü–Η–Κ–Μ–Α–Φ–Η¬Μ, –≤–Η–Κ–Ψ–Ϋ―É―é―΅–Η –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è –Ω―•–¥ ―΅–Α―¹ –Ω―Ä–Ψ―¹―²–Ψ―é ―¹–Η―¹―²–Β–Φ–Η. –Δ–Ψ–Φ―É ―½―Ö–Ϋ―• ―Ä–Β–Α–Μ―•–Ζ–Α―Ü―•―½ –Ω―•–¥ –≤–Η–≥–Μ―è–¥–Ψ–Φ –Β–Κ―Ä–Α–Ϋ–Ϋ–Η―Ö –Ζ–Α―¹―²–Α–≤–Ψ–Κ –¥–Ψ–≤–Ψ–Μ―• –Ω–Ψ―à–Η―Ä–Β–Ϋ―•.

–Θ –≥–Α–Μ―É–Ζ―• –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ ―î ―¹–Ω–Β―Ü―•–Α–Μ―¨–Ϋ―• –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Ω―Ä–Η―¹―²―Ä–Ψ―½, ―â–Ψ –Ζ–Α–Ι–Φ–Α―é―²―¨ ―¹–≤–Ψ―½ –Ϋ―•―à―•. –Ü ―Ö–Ψ―΅–Α –≤–Ψ–Ϋ–Η –Ϋ–Β ―î –Ω―Ä–Β–¥–Φ–Β―²–Ϋ–Ψ-–Ψ―Ä―•―î–Ϋ―²–Ψ–≤–Α–Ϋ–Η–Φ–Η, ―²–Α –≤―¹–Β –Ε –≤–Ψ–Ϋ–Η –Ζ–Α–Ζ–≤–Η―΅–Α–Ι –Ζ–Α―¹―²–Ψ―¹–Ψ–≤―É―é―²―¨―¹―è –Μ–Η―à–Β –¥–Μ―è –Ω–Β–≤–Ϋ–Η―Ö –Κ–Μ–Α―¹―•–≤ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Ζ–Α–¥–Α―΅.

–û–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è –Ζ–Α–≥–Α–Μ―¨–Ϋ–Ψ–≥–Ψ –Ω―Ä–Η–Ζ–Ϋ–Α―΅–Β–Ϋ–Ϋ―è –Ϋ–Α –≥―Ä–Α―³―•―΅–Ϋ–Η―Ö ―¹–Ω―•–≤–Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α―Ö (GPGPU) –î–Ψ–Κ–Μ–Α–¥–Ϋ―•―à–Β: GPGPU –£―•–¥–Β–Ψ–Κ–Α―Ä―²–Α Nvidia Tesla –½–Α–≥–Α–Μ―¨–Ϋ―• –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è –Ϋ–Α –≥―Ä–Α―³―•―΅–Ϋ–Η―Ö –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α―Ö ―Ü–Β –Ω–Ψ―Ä―•–≤–Ϋ―è–Ϋ–Ψ –Ϋ–Ψ–≤–Α ―²–Β–Ϋ–¥–Β–Ϋ―Ü―•―è –≤ –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ―•–Ι ―•–Ϋ–Ε–Β–Ϋ–Β―Ä―•―½. –™―Ä–Α―³―•―΅–Ϋ―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Η βÄî –¥–Ψ–Ω–Ψ–Φ―•–Ε–Ϋ―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Η, ―â–Ψ –±―É–Μ–Η ―¹–Η–Μ―¨–Ϋ–Ψ –Ψ–Ω―²–Η–Φ―•–Ζ–Ψ–≤–Α–Ϋ―• –¥–Μ―è –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ–Ψ―½ –≥―Ä–Α―³―•–Κ–Η .[ 32] –Φ–Α―²―Ä–Η―Ü―è–Φ–Η –≤ –Μ―•–Ϋ―•–Ι–Ϋ―•–Ι –Α–Μ–≥–Β–±―Ä―• .

–ù–Α –Ω–Ψ―΅–Α―²–Κ―É, –≤―•–¥–Β–Ψ–Κ–Α―Ä―²–Η –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É–≤–Α–Μ–Η –≥―Ä–Α―³―•―΅–Ϋ―• API –¥–Μ―è –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è ―¹–≤–Ψ―½ –Ω―Ä–Ψ–≥―Ä–Α–Φ. –©–Ψ–Ω―Ä–Α–≤–¥–Α ―²–Β–Ω–Β―Ä –Ζ'―è–≤–Η–Μ–Ψ―¹―¨ –Κ―•–Μ―¨–Κ–Α –Ϋ–Ψ–≤–Η―Ö –Φ–Ψ–≤ –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è ―²–Α –Ω–Μ–Α―²―³–Ψ―Ä–Φ –Ζ–±―É–¥–Ψ–≤–Α–Ϋ–Η―Ö –¥–Μ―è –≤–Η–Κ–Ψ–Ϋ–Α–Ϋ–Ϋ―è –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ –Ζ–Α–≥–Α–Μ―¨–Ϋ–Ψ–≥–Ψ –Ω―Ä–Η–Ζ–Ϋ–Α―΅–Β–Ϋ–Ϋ―è –Ϋ–Α –≤―•–¥–Β–Ψ–Κ–Α―Ä―²–Α―Ö ―è–Κ –Ϋ–Α ―¹–Β―Ä–Β–¥–Ψ–≤–Η―â–Α―Ö CUDA –¥–Μ―è Nvidia ―²–Α–Κ ―• –Ϋ–Α CMT –¥–Μ―è AMD . –Ü–Ϋ―à–Η–Φ–Η –Φ–Ψ–≤–Α–Φ–Η –¥–Μ―è –Ζ–Α–≥–Α–Μ―¨–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ –Ϋ–Α –≤―•–¥–Β–Ψ–Κ–Α―Ä―²–Α―Ö ―î BrookGPU , PeakStream , ―²–Α RapidMind . Nvidia ―²–Α–Κ–Ψ–Ε –≤–Η–Ω―É―¹―²–Η–Μ–Α ―¹–Ω–Β―Ü―•–Α–Μ―¨–Ϋ―• –Ζ–Α―¹–Ψ–±–Η –¥–Μ―è –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ –Ϋ–Α ―¹–≤–Ψ―½―Ö –≤―•–¥–Β–Ψ–Κ–Α―Ä―²–Α―Ö ―¹–Β―Ä―•―½ Tesla .

–ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Φ–Ψ–≤–Η –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è, –±―•–±–Μ―•–Ψ―²–Β–Κ–Η, API ―• –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Φ–Ψ–¥–Β–Μ―• –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è, –±―É–Μ–Η ―¹―²–≤–Ψ―Ä–Β–Ϋ―• –¥–Μ―è –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤. –£ ―Ü―•–Μ–Ψ–Φ―É ―½―Ö –Φ–Ψ–Ε–Ϋ–Α –Ω–Ψ–¥―•–Μ–Η―²–Η –Ϋ–Α –Κ–Μ–Α―¹–Η, –Ζ–Α―¹–Ϋ–Ψ–≤–Α–Ϋ―• –Ϋ–Α –Ω―Ä–Η–Ω―É―â–Β–Ϋ–Ϋ―è―Ö, –Ψ―¹–Ϋ–Ψ–≤–Α ―è–Κ–Η―Ö –Μ–Β–Ε–Η―²―¨ –≤ –±―É–¥–Ψ–≤―•, –Ζ–Α–≥–Α–Μ―¨–Ϋ–Ψ―½ –Ω–Α–Φ'―è―²―• –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Ψ―½ –Ω–Α–Φ'―è―²―•, ―Ä–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Ψ―½ –Ω–Α–Φ'―è―²―•, –Α–±–Ψ –Ζ–Α–≥–Α–Μ―¨–Ϋ–Ψ―½ ―Ä–Ψ–Ζ–Ω–Ψ–¥―•–Μ–Β–Ϋ–Ψ―½ –Ω–Α–Φ'―è―²―•. –û–¥–Ϋ―•―î―é –Ζ –Κ–Ψ–Ϋ―Ü–Β–Ω―Ü―•–Ι, ―è–Κ―• –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―é―²―¨―¹―è –≤ –Ω―Ä–Ψ–≥―Ä–Α–Φ–Α―Ö –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ–≥–Ψ –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è, ―î –Κ–Ψ–Ϋ―Ü–Β–Ω―Ü―•―è –Φ–Α–Ι–±―É―²–Ϋ–Ψ―¹―²―• [en]

CAPS entreprise ―²–Α Pathscale ―²–Α–Κ–Ψ–Ε –Κ–Ψ–Ψ―Ä–¥–Η–Ϋ―É―é―²―¨ –Ζ―É―¹–Η–Μ–Μ―è, ―â–Ψ–±–Η –Ζ―Ä–Ψ–±–Η―²–Η –¥–Η―Ä–Β–Κ―²–Η–≤–Η –≥―•–±―Ä–Η–¥–Ϋ–Ψ–≥–Ψ –±–Α–≥–Α―²–Ψ―è–¥–Β―Ä–Ϋ–Ψ–≥–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ–≥–Ψ –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è (–Α–Ϋ–≥–Μ. hybrid multi-core parallel programming, HMPP ) –≤―•–¥–Κ―Ä–Η―²–Η–Φ ―¹―²–Α–Ϋ–¥–Α―Ä―²–Ψ–Φ –Ω―•–¥ –Ϋ–Α–Ζ–≤–Ψ―é OpenHMPP . –€–Ψ–¥–Β–Μ―¨ –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è –Ϋ–Α –Ψ―¹–Ϋ–Ψ–≤―• –¥–Η―Ä–Β–Κ―²–Η–≤ OpenHMPP –Ω―Ä–Ψ–Ω–Ψ–Ϋ―É―î ―¹–Η–Ϋ―²–Α–Κ―¹–Η―¹ –Β―³–Β–Κ―²–Η–≤–Ϋ–Ψ–≥–Ψ ―Ä–Ψ–Ζ–≤–Α–Ϋ―²–Α–Ε–Β–Ϋ–Ϋ―è –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ –Ϋ–Α –Α–Ω–Α―Ä–Α―²–Ϋ–Η―Ö –Ω―Ä–Η―¹–Κ–Ψ―Ä―é–≤–Α―΅–Α―Ö ―• –Ψ–Ω―²–Η–Φ―•–Ζ–Α―Ü―•―é –Ω–Β―Ä–Β–Φ―•―â–Β–Ϋ–Ϋ―è –¥–Α–Ϋ–Η―Ö –≤/–Ζ –Α–Ω–Α―Ä–Α―²–Ϋ–Ψ―½ –Ω–Α–Φ'―è―²―•. –î–Η―Ä–Β–Κ―²–Η–≤–Η OpenHMPP –Ψ–Ω–Η―¹―É―é―²―¨ –≤–Η–Κ–Μ–Η–Κ –≤―•–¥–¥–Α–Μ–Β–Ϋ–Η―Ö –Ω―Ä–Ψ―Ü–Β–¥―É―Ä (–Α–Ϋ–≥–Μ. remote procedure call, RPC ) –Ϋ–Α –Ω―Ä–Η―¹–Κ–Ψ―Ä―é–≤–Α–Ϋ―• (–Ϋ–Α–Ω―Ä–Η–Κ–Μ–Α–¥, –™–ü ) –Α–±–Ψ, –≤ –Ζ–Α–≥–Α–Μ―¨–Ϋ―•―à–Ψ–Φ―É –≤–Η–Ω–Α–¥–Κ―É, –Ϋ–Α –Ϋ–Α–±–Ψ―Ä―• ―è–¥–Β―Ä. –Π―• –¥–Η―Ä–Β–Κ―²–Η–≤–Η ―Ä–Ψ–±–Μ―è―²―¨ –Ϋ–Ψ―²–Α―²–Κ–Η –≤ –Κ–Ψ–¥―• C –Α–±–Ψ Fortran –¥–Μ―è –Ψ–Ω–Η―¹―É –¥–≤–Ψ―Ö –Ϋ–Α–±–Ψ―Ä―•–≤ ―³―É–Ϋ–Κ―Ü―•–Ψ–Ϋ–Α–Μ―¨–Ϋ–Η―Ö –Φ–Ψ–Ε–Μ–Η–≤–Ψ―¹―²–Β–Ι: ―Ä–Ψ–Ζ–≤–Α–Ϋ―²–Α–Ε–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ―Ü–Β–¥―É―Ä (―â–Ψ –Ω–Ψ–Ζ–Ϋ–Α―΅–Α―é―²―¨―¹―è codelets ) –Ϋ–Α –≤―•–¥–¥–Α–Μ–Β–Ϋ–Η–Ι –Ω―Ä–Η―¹―²―Ä―•–Ι, ―²–Α –Ψ–Ω―²–Η–Φ―•–Ζ–Α―Ü―•―é –Ω–Β―Ä–Β–¥–Α–≤–Α–Ϋ–Ϋ―è –¥–Α–Ϋ–Η―Ö –Φ―•–Ε –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Ψ―é –Ω–Α–Φ'―è―²―²―é –Π–ü ―²–Α –Ω–Α–Φ'―è―²―²―é –Ω―Ä–Η―¹–Κ–Ψ―Ä―é–≤–Α―΅–Α.

–ê–≤―²–Ψ–Φ–Α―²–Η―΅–Ϋ–Β ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é–≤–Α–Ϋ–Ϋ―è –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Ψ―½ –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η –Κ–Ψ–Φ–Ω―•–Μ―è―²–Ψ―Ä–Ψ–Φ ―î ―¹–≤―è―²–Η–Φ –≥―Ä–Α–Α–Μ–Β–Φ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨. –ù–Β–Ζ–≤–Α–Ε–Α―é―΅–Η –Ϋ–Α –¥–Β―¹―è―²–Η–Μ―•―²―²―è ―Ä–Ψ–±–Ψ―²–Η –¥–Ψ―¹–Μ―•–¥–Ϋ–Η–Κ–Α–Φ–Η –Κ–Ψ–Φ–Ω―•–Μ―è―²–Ψ―Ä―•–≤, –Α–≤―²–Ψ–Φ–Α―²–Η―΅–Ϋ–Β ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é–≤–Α–Ϋ–Ϋ―è –Φ–Α―î –Ψ–±–Φ–Β–Ε–Β–Ϋ–Η–Ι ―É―¹–Ω―•―Ö.

–™–Ψ–Μ–Ψ–≤–Ϋ―• –Φ–Ψ–≤–Η –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ–≥–Ψ –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è –Ζ–Α–Μ–Η―à–Α―é―²―¨―¹―è –Α–±–Ψ ―è–≤–Ϋ–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η–Φ–Η –Α–±–Ψ (–≤ –Κ―Ä–Α―â–Ψ–Φ―É –≤–Η–Ω–Α–¥–Κ―É), ―΅–Α―¹―²–Κ–Ψ–≤–Ψ –Ϋ–Β―è–≤–Ϋ–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η–Φ–Η, –≤ ―è–Κ–Η―Ö –Ω―Ä–Ψ–≥―Ä–Α–Φ―•―¹―² –¥–Α―î –¥–Η―Ä–Β–Κ―²–Η–≤–Η –¥–Μ―è ―Ä–Ψ–Ζ–Ω–Α―Ä–Α–Μ–Β–Μ―é–≤–Α–Ϋ–Ϋ―è –Κ–Ψ–Φ–Ω―•–Μ―è―²–Ψ―Ä―É. –ü–Ψ–≤–Ϋ―•―¹―²―é ―è–≤–Ϋ–Ψ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Φ–Ψ–≤–Η ―•―¹–Ϋ―É―é―²―¨ βÄî SISAL [en] Haskell , SequenceL [en] System C (–¥–Μ―è –ü–ö–£–€ ), Mitrion-C , VHDL , ―• Verilog .

–½ ―Ä–Ψ―¹―²–Ψ–Φ ―¹–Κ–Μ–Α–¥–Ϋ–Ψ―¹―²―• –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ–Ψ―½ ―¹–Η―¹―²–Β–Φ–Η ―¹–Β―Ä–Β–¥–Ϋ―•–Ι –Ϋ–Α―Ä–Ψ–±―•―²–Ψ–Κ –Φ―•–Ε –≤―•–¥–Φ–Ψ–≤–Α–Φ–Η , ―è–Κ –Ω―Ä–Α–≤–Η–Μ–Ψ, –Ζ–Φ–Β–Ϋ―à―É―î―²―¨―¹―è. –ö–Ψ–Ϋ―²―Ä–Ψ–Μ―¨–Ϋ―• ―²–Ψ―΅–Κ–Η –Ω―Ä–Ψ–≥―Ä–Α–Φ–Η βÄî ―Ü–Β –Φ–Β―²–Ψ–¥, –Ζ–Α –¥–Ψ–Ω–Ψ–Φ–Ψ–≥–Ψ―é ―è–Κ–Ψ–≥–Ψ –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ–Α ―¹–Η―¹―²–Β–Φ–Α ―Ä–Ψ–±–Η―²―¨ ¬Ϊ–Ζ–Ϋ―•–Φ–Ψ–Κ¬Μ –Ζ–Α―¹―²–Ψ―¹―É–Ϋ–Κ―É, βÄî –Ζ–Α–Ω–Η―¹ ―É―¹―•―Ö –Ω–Ψ―²–Ψ―΅–Ϋ–Η―Ö –≤–Η–¥―•–Μ–Β–Ϋ–Η―Ö ―Ä–Β―¹―É―Ä―¹―•–≤ ―• ―¹―²–Α–Ϋ―•–≤ –Ζ–Φ―•–Ϋ–Ϋ–Η―Ö, ―¹―Ö–Ψ–Ε–Η–Ι –Ϋ–Α –¥–Α–Φ–Ω ―è–¥―Ä–Α [en] –≤–Η―¹–Ψ–Κ–Ψ–Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ .

–û―¹–Κ―•–Μ―¨–Κ–Η –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Η ―¹―²–Α―é―²―¨ –≤―¹–Β –Κ―Ä–Α―â―• ―• ―à–≤–Η–¥―à―•, ―¹―²–Α―î –Φ–Ψ–Ε–Μ–Η–≤–Η–Φ –≤–Η―Ä―•―à–Η―²–Η –Ω―Ä–Ψ–±–Μ–Β–Φ–Η, ―è–Κ―• ―Ä–Α–Ϋ―•―à–Β –Ζ–Α–Ι–Φ–Α–Μ–Η –±–Α–≥–Α―²–Ψ ―΅–Α―¹―É. –ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è –≤–Η–Κ–Ψ―Ä–Η―¹―²–Ψ–≤―É―î―²―¨―¹―è –≤ ―Ä―•–Ζ–Ϋ–Η―Ö ―¹―³–Β―Ä–Α―Ö –Ε–Η―²―²―è, –≤―•–¥ –±―•–Ψ―•–Ϋ―³–Ψ―Ä–Φ–Α―²–Η–Κ–Η (–Ζ–≥–Ψ―Ä―²–Α–Ϋ–Ϋ―è –±―•–Μ–Κ―•–≤ ―• –Α–Ϋ–Α–Μ―•–Ζ –Ω–Ψ―¹–Μ―•–¥–Ψ–≤–Ϋ–Ψ―¹―²―•) –¥–Ψ –Β–Κ–Ψ–Ϋ–Ψ–Φ―•–Κ–Η (―³―•–Ϋ–Α–Ϋ―¹–Ψ–≤–Ψ―½ –Φ–Α―²–Β–Φ–Α―²–Η–Κ–Η). –ù–Α–Ι–±―•–Μ―¨―à –Ω–Ψ―à–Η―Ä–Β–Ϋ–Η–Φ–Η ―²–Η–Ω–Α–Φ–Η –Ω―Ä–Ψ–±–Μ–Β–Φ, –≤–Η―è–≤–Μ–Β–Ϋ–Η―Ö –≤ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ–Η―Ö ―î:

–ü–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ―• –Ψ–±―΅–Η―¹–Μ–Β–Ϋ–Ϋ―è ―²–Α–Κ–Ψ–Ε –Φ–Ψ–Ε―É―²―¨ –±―É―²–Η –Ζ–Α―¹―²–Ψ―¹–Ψ–≤–Α–Ϋ―• –¥–Ψ –Ω―Ä–Ψ–Β–Κ―²―É–≤–Α–Ϋ–Ϋ―è –≤―•–¥–Φ–Ψ–≤–Ψ―¹―²―•–Ι–Κ–Η―Ö –Ψ–±―΅–Η―¹–Μ―é–≤–Α–Μ―¨–Ϋ–Η―Ö ―¹–Η―¹―²–Β–Φ, –Ζ–Ψ–Κ―Ä–Β–Φ–Α, –Ζ–Α –¥–Ψ–Ω–Ψ–Φ–Ψ–≥–Ψ―é Lockstep ―¹–Η―¹―²–Β–Φ–Η, ―â–Ψ –≤–Η–Κ–Ψ–Ϋ―É―é―²―¨ ―²―• –Ε –Ψ–Ω–Β―Ä–Α―Ü―•―½ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ. –Π–Β –Ζ–Α–±–Β–Ζ–Ω–Β―΅―É―î –Ϋ–Α–¥–Μ–Η―à–Κ–Ψ–≤―•―¹―²―¨ ―É ―Ä–Α–Ζ―• –Ω–Α–¥―•–Ϋ–Ϋ―è –Ψ–¥–Ϋ–Ψ–≥–Ψ –Ζ –Κ–Ψ–Φ–Ω–Ψ–Ϋ–Β–Ϋ―²―•–≤ ―• ―²–Α–Κ–Ψ–Ε –¥–Ψ–Ζ–≤–Ψ–Μ―è―î –Α–≤―²–Ψ–Φ–Α―²–Η―΅–Ϋ–Ψ –≤–Η–Ζ–Ϋ–Α―΅–Α―²–Η ―²–Α –≤–Η–Ω―Ä–Α–≤–Μ―è―²–Η –Ω–Ψ–Φ–Η–Μ–Κ–Η ―è–Κ―â–Ψ ―Ä–Β–Ζ―É–Μ―¨―²–Α―²–Η ―Ä―•–Ζ–Ϋ―è―²―¨―¹―è. –Π―• –Φ–Β―²–Ψ–¥–Η –Φ–Ψ–Ε―É―²―¨ –±―É―²–Η –≤–Η–Κ–Ψ―Ä–Η―¹―²–Α–Ϋ―•, ―â–Ψ–± –¥–Ψ–Ω–Ψ–Φ–Ψ–≥―²–Η –Ζ–Α–Ω–Ψ–±―•–≥―²–Η –Ω–Ψ–Ψ–¥–Η–Ϋ–Ψ–Κ–Η–Φ –Ω–Ψ–¥―•―è–Φ, ―è–Κ―• –≤–Η–Κ–Μ–Η–Κ–Α―é―²―¨ ―²–Η–Φ―΅–Α―¹–Ψ–≤―• –Ω–Ψ–Φ–Η–Μ–Κ–Η. –Ξ–Ψ―΅–Α –¥–Ψ–¥–Α―²–Κ–Ψ–≤―• –Ζ–Α―Ö–Ψ–¥–Η –Φ–Ψ–Ε―É―²―¨ –Ζ–Ϋ–Α–¥–Ψ–±–Η―²–Η―¹―è ―É –≤–±―É–¥–Ψ–≤–Α–Ϋ–Η―Ö –Α–±–Ψ ―¹–Ω–Β―Ü―•–Α–Μ―•–Ζ–Ψ–≤–Α–Ϋ–Η―Ö ―¹–Η―¹―²–Β–Φ–Α―Ö, ―Ü–Β–Ι –Φ–Β―²–Ψ–¥ –Φ–Ψ–Ε–Β –Ζ–Α–±–Β–Ζ–Ω–Β―΅–Η―²–Η –Β–Κ–Ψ–Ϋ–Ψ–Φ―•―΅–Ϋ–Ψ –Β―³–Β–Κ―²–Η–≤–Ϋ–Η–Ι –Ω―•–¥―Ö―•–¥ –¥–Ψ –¥–Ψ―¹―è–≥–Ϋ–Β–Ϋ–Ϋ―è –Ω-–Φ–Ψ–¥―É–Μ―¨–Ϋ–Ψ―½ –Ϋ–Α–¥–Φ―•―Ä–Ϋ–Ψ―¹―²―• –≤ –Κ–Ψ–Φ–Β―Ä―Ü―•–Ι–Ϋ–Η―Ö ―¹–Η―¹―²–Β–Φ–Α―Ö.

ILLIAC IV [en] [ 33] –£–Η―²–Ψ–Κ–Η ―•―¹―²–Η–Ϋ–Ϋ–Ψ―½ (MIMD) –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ―¹―²―• –Ω―•―à–Μ–Η –≤―•–¥ –¦―É―½–¥–Ε―• –Λ–Β–¥–Β―Ä―•–Κ–Ψ –€–Β–Ϋ–Α–±―Ä–Β–Α ―• –Ι–Ψ–≥–Ψ ¬Ϊ–ï―¹–Κ―•–Ζ―É –ê–Ϋ–Α–Μ―•―²–Η―΅–Ϋ–Ψ–≥–Ψ –¥–≤–Η–≥―É–Ϋ–Α –£–Η–Ϋ–Α–Ι–¥–Β–Ϋ–Ψ–≥–Ψ –ß–Α―Ä–Μ―¨–Ζ–Ψ–Φ –ë–Β–±–±―•–¥–Ε–Β–Φ¬Μ.

–Θ –Κ–≤―•―²–Ϋ―• 1958 ―Ä–Ψ–Κ―É –Γ. –™―•–Μ–Μ (Ferranti) –Ψ–±–≥–Ψ–≤–Ψ―Ä–Η–Μ–Η –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Β –Ω―Ä–Ψ–≥―Ä–Α–Φ―É–≤–Α–Ϋ–Ϋ―è ―• –Ϋ–Β–Ψ–±―Ö―•–¥–Ϋ―•―¹―²―¨ ―Ä–Ψ–Ζ–≥–Α–Μ―É–Ε–Β–Ϋ–Ϋ―è ―• –Ψ―΅―•–Κ―É–≤–Α–Ϋ–Ϋ―è. –ö―Ä―•–Φ ―²–Ψ–≥–Ψ, –≤ 1958 ―Ä–Ψ―Ü―• –¥–Ψ―¹–Μ―•–¥–Ϋ–Η–Κ–Η IBM –î–Ε–Ψ–Ϋ –ö–Ψ–Κ ―• –î–Α–Ϋ―•–Β–Μ―¨ –Γ–Μ–Ψ―²–Ϋ―•–Κ –≤–Ω–Β―Ä―à–Β –Ψ–±–≥–Ψ–≤–Ψ―Ä–Η–Μ–Η –≤–Η–Κ–Ψ―Ä–Η―¹―²–Α–Ϋ–Ϋ―è –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ―É –≤ ―΅–Η―¹–Μ–Β–Ϋ–Ϋ–Η―Ö ―Ä–Ψ–Ζ―Ä–Α―Ö―É–Ϋ–Κ–Α―Ö. Burroughs Corporation –Ω―Ä–Β–¥―¹―²–Α–≤–Η–Μ–Α D825 –≤ 1962 ―Ä–Ψ―Ü―•, ―΅–Ψ―²–Η―Ä―¨–Ψ―Ö –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Ϋ–Η–Ι –Κ–Ψ–Φ–Ω'―é―²–Β―Ä, –≤―•–Ϋ –Ϋ–Α–¥–Α–≤–Α–≤ –¥–Ψ―¹―²―É–Ω –¥–Ψ 16 –Φ–Ψ–¥―É–Μ―•–≤ –Ω–Α–Φ'―è―²―• ―΅–Β―Ä–Β–Ζ –Κ–Ψ–Φ―É―²–Α―²–Ψ―Ä. –Θ 1967 ―Ä–Ψ―Ü―• –ê–Φ–¥–Α–Μ ―• –Γ–Μ–Ψ―²–Ϋ―•–Κ –Ψ–Ω―É–±–Μ―•–Κ―É–≤–Α–Μ–Η –¥–Η―¹–Κ―É―¹―•―é –Ω―Ä–Ψ –Φ–Ψ–Ε–Μ–Η–≤―•―¹―²―¨ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ―½ –Ψ–±―Ä–Ψ–±–Κ–Η –Ϋ–Α –Κ–Ψ–Ϋ―³–Β―Ä–Β–Ϋ―Ü―•―½ –ê–Φ–Β―Ä–Η–Κ–Α–Ϋ―¹―¨–Κ–Ψ―½ ―³–Β–¥–Β―Ä–Α―Ü―•―½ ―²–Ψ–≤–Α―Ä–Η―¹―²–≤ –Ζ –Ψ–±―Ä–Ψ–±–Κ–Η ―•–Ϋ―³–Ψ―Ä–Φ–Α―Ü―•―½. –Γ–Α–Φ–Β –≤ ―Ö–Ψ–¥―• ―Ü―•―î―½ –¥–Η―¹–Κ―É―¹―•―½ –±―É–≤ –Ω―Ä–Η–¥―É–Φ–Α–Ϋ–Η–Ι –Ζ–Α–Κ–Ψ–Ϋ –ê–Φ–¥–Α–Μ―è, ―â–Ψ–± –≤–Η–Ζ–Ϋ–Α―΅–Η―²–Η –Φ–Β–Ε―É –Ω―Ä–Η―¹–Κ–Ψ―Ä–Β–Ϋ–Ϋ―è –Ζ–Α–≤–¥―è–Κ–Η –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ―¹―²―•.

–Θ 1969 ―Ä–Ψ―Ü―• –Κ–Ψ–Φ–Ω–Α–Ϋ―•―è Honeywell –Ω―Ä–Β–¥―¹―²–Α–≤–Η–Μ–Α ―¹–≤–Ψ―é –Ω–Β―Ä―à―É Multics, ―¹–Η–Φ–Β―²―Ä–Η―΅–Ϋ―É ―¹–Η―¹―²–Β–Φ―É, –Φ―É–Μ―¨―²–Η–Φ―•–Κ―Ä–Ψ–Κ–Ψ–Ϋ―²―Ä–Ψ–Μ–Μ–Β―Ä–Ϋ―É, –Ζ–¥–Α―²–Ϋ―É –Ω―Ä–Α―Ü―é–≤–Α―²–Η –¥–Ψ –≤–Ψ―¹―¨–Φ–Η –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤ –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Ψ. –½ 1970-―Ö ―Ä–Ψ–Κ―•–≤ –±–Α–≥–Α―²–Ψ–Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Ϋ–Η–Ι –Ω―Ä–Ψ–Β–Κ―² –Θ–Ϋ―•–≤–Β―Ä―¹–Η―²–Β―²―É –ö–Α―Ä–Ϋ–Β–≥―•-–€–Β–Μ–Μ–Ψ–Ϋ–Α, –±―É–≤ –Ψ–¥–Ϋ–Η–Φ –Ζ –Ω–Β―Ä―à–Η―Ö –Φ―É–Μ―¨―²–Η–Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤ –Ζ –±―•–Μ―¨―à –Ϋ―•–Ε –Κ―•–Μ―¨–Κ–Ψ–Φ–Α –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α–Φ–Η.

–Ü―¹―²–Ψ―Ä―•―é –Ω–Α―Ä–Α–Μ–Β–Μ―¨–Ϋ–Η―Ö –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤ SIMD –Φ–Ψ–Ε–Ϋ–Α –Ω―Ä–Ψ―¹―²–Β–Ε–Η―²–Η –Ζ 1970-―Ö ―Ä–Ψ–Κ―•–≤. –€–Ψ―²–Η–≤–Α―Ü―•―î―é ―Ä–Α–Ϋ–Ϋ―•―Ö –Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤ SIMD –±―É–≤ –Α–Φ–Ψ―Ä―²–Η–Ζ―É–≤–Α―²–Η –Ζ–Α―²―Ä–Η–Φ–Κ―É ―É–Ω―Ä–Α–≤–Μ―•–Ϋ–Ϋ―è –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–Α –Κ―•–Μ―¨–Κ–Ψ–Φ–Α ―•–Ϋ―¹―²―Ä―É–Κ―Ü―•―è–Φ–Η. –Θ 1964 ―Ä–Ψ―Ü―• –Γ–Μ–Ψ―²–Ϋ―•–Κ –Ζ–Α–Ω―Ä–Ψ–Ω–Ψ–Ϋ―É–≤–Α–≤ –±―É–¥―É–≤–Α―²–Η –€–£–Γ –¥–Μ―è –¦―•–≤–Β―Ä–Φ–Ψ―Ä―¹―¨–Κ–Ψ―½ –Ϋ–Α―Ü―•–Ψ–Ϋ–Α–Μ―¨–Ϋ–Ψ―½ –Μ–Α–±–Ψ―Ä–Α―²–Ψ―Ä―•―½. –ô–Ψ–≥–Ψ –Ω―Ä–Ψ–Β–Κ―² –±―É–≤ –Ω―Ä–Ψ―³―•–Ϋ–Α–Ϋ―¹–Ψ–≤–Α–Ϋ–Η–Ι –£–£–Γ –Γ–®–ê. –ö–Μ―é―΅–Β–Φ –¥–Ψ –Ι–Ψ–≥–Ψ –Κ–Ψ–Ϋ―¹―²―Ä―É–Κ―Ü―•―½ –±―É–≤ –¥–Ψ―¹–Η―²―¨ –≤–Η―¹–Ψ–Κ–Η–Ι –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ, –Α–Ε –¥–Ψ 256 –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤, ―â–Ψ –¥–Ψ–Ζ–≤–Ψ–Μ–Η–Μ–Ψ –Φ–Α―à–Η–Ϋ–Α–Φ –Ω―Ä–Α―Ü―é–≤–Α―²–Η –Ϋ–Α –≤–Β–Μ–Η–Κ–Η―Ö –Ϋ–Α–±–Ψ―Ä–Α―Ö –¥–Α–Ϋ–Η―Ö –≤ ―²–Ψ–Φ―É, ―â–Ψ –Ω―•–Ζ–Ϋ―•―à–Β –±―É–¥–Β –≤―•–¥–Ψ–Φ–Β ―è–Κ –≤–Β–Κ―²–Ψ―Ä –Ψ–±―Ä–Ψ–±–Κ–Η. –ü―Ä–Ψ―²–Β, ILLIAC IV –±―É–≤ –Ϋ–Α–Ζ–≤–Α–Ϋ–Η–Ι ¬Ϊ―¹–Α–Φ–Η–Φ ―¹―É–Φ–Ϋ–Ψ–Ζ–≤―•―¹–Ϋ–Ψ―½ ―¹―É–Ω–Β―Ä–Κ–Ψ–Φ–Ω'―é―²–Β―Ä―•–≤¬Μ, ―²–Ψ–Φ―É ―â–Ψ –Ω―Ä–Ψ–Β–Κ―² –±―É–≤ ―²―•–Μ―¨–Κ–Η –Ϋ–Α ―΅–≤–Β―Ä―²―¨ –Ζ–Α–≤–Β―Ä―à–Β–Ϋ–Η–Ι, –Α–Μ–Β –Ω―•―à–Μ–Ψ 11 ―Ä–Ψ–Κ―•–≤ ―• –Κ–Ψ―à―²―É–≤–Α–≤ –Φ–Α–Ι–Ε–Β –≤ ―΅–Ψ―²–Η―Ä–Η ―Ä–Α–Ζ–Η –±―•–Μ―¨―à–Β –Ω–Β―Ä–≤―•―¹–Ϋ–Ψ―½ –Ψ―Ü―•–Ϋ–Κ–Η. –ö–Ψ–Μ–Η –≤―•–Ϋ, –Ϋ–Α―Ä–Β―à―²―•, –≥–Ψ―²–Ψ–≤–Η–Ι –¥–Ψ –Ζ–Α–Ω―É―¹–Κ―É (–Ω–Β―Ä―à–Η–Ι ―Ä–Β–Α–Μ―¨–Ϋ–Β –Ζ–Α―¹―²–Ψ―¹―É–≤–Α–Ϋ–Ϋ―è –≤ 1976 ―Ä–Ψ―Ü―•) –≤―•–Ϋ –Ω―Ä–Ψ–≥―Ä–Α–≤–Α–≤ ―•―¹–Ϋ―É―é―΅–Η–Φ –Κ–Ψ–Φ–Β―Ä―Ü―•–Ι–Ϋ–Η–Φ ―¹―É–Ω–Β―Ä–Κ–Ψ–Φ–Ω'―é―²–Β―Ä–Α–Φ, ―²–Α–Κ–Η–Φ ―è–Κ Cray-1.

βÜë Almasi, G.S. and A. Gottlieb (1989). Highly Parallel Computing

βÜë S.V. Adve et al. (–¦–Η―¹―²–Ψ–Ω–Α–¥ 2008). ¬ΪParallel Computing Research at Illinois: The UPCRC Agenda¬Μ [–ê―Ä―Ö―•–≤–Ψ–≤–Α–Ϋ–Ψ 9 –≥―Ä―É–¥–Ϋ―è 2008 ―É Wayback Machine .] (PDF). Parallel@Illinois, University of Illinois at Urbana-Champaign. ¬Ϊ–û―¹–Ϋ–Ψ–≤–Ϋ―• ―²–Β―Ö–Ϋ–Ψ–Μ–Ψ–≥―•―½ –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Ψ―¹―²―• –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ βÄî –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è ―΅–Α―¹―²–Ψ―²–Η ―²–Α–Κ―²–Ψ–≤–Ψ–≥–Ψ –≥–Β–Ϋ–Β―Ä–Α―²–Ψ―Ä–Α, ―²–Α ―Ö–Η―²―Ä―•―à―•, –Ω―Ä–Ψ―²–Β –≤―•–¥–Ω–Ψ–≤―•–¥–Ϋ–Ψ –Ϋ–Α–±–Α–≥–Α―²–Ψ ―¹–Κ–Μ–Α–¥–Ϋ―•―à―• –Α―Ä―Ö―•―²–Β–Κ―²―É―Ä–Η, ―¹―¨–Ψ–≥–Ψ–¥–Ϋ―• ―¹―²–Η–Κ–Α―é―²―¨―¹―è –Ζ ―²–Α–Κ –Ζ–≤–Α–Ϋ–Ψ―é ―¹―²―•–Ϋ–Ψ―é –Ω–Ψ―²―É–Ε–Ϋ–Ψ―¹―²―•. –ö–Ψ–Φ–Ω'―é―²–Β―Ä–Ϋ–Α –Ω―Ä–Ψ–Φ–Η―¹–Μ–Ψ–≤―•―¹―²―¨ –Ω―Ä–Η–Ι–Ϋ―è–Μ–Α ―³–Α–Κ―², ―â–Ψ –Φ–Α–Ι–±―É―²–Ϋ―• –Ζ―Ä–Ψ―¹―²–Α–Ϋ–Ϋ―è –Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Ψ―¹―²―• –Ψ–±―΅–Η―¹–Μ–Β–Ϋ―¨ –±―É–¥―É―²―¨ –Ω–Ψ–≤'―è–Ζ–Α–Ϋ―• –Ζ―• –Ζ―Ä–Ψ―¹―²–Α–Ϋ–Ϋ―è–Φ –Κ―•–Μ―¨–Κ–Ψ―¹―²―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä―•–≤ (―΅–Η ―è–¥–Β―Ä), –Α–Ϋ―•–Ε –Ζ―• ―¹–Ω―Ä–Ψ–±–Α–Φ–Η –Ζ–Φ―É―¹–Η―²–Η –Ψ–¥–Ϋ–Β ―è–¥―Ä–Ψ –Ω―Ä–Α―Ü―é–≤–Α―²–Η ―à–≤–Η–¥―à–Β¬Μ.

βÜë Asanovic et al. –Γ―²–Α―Ä–Η–Ι –Ω―Ä–Η–Ϋ―Ü–Η–Ω –Β–Κ–Ψ–Ϋ–Ψ–Φ―•―½: –ï–Μ–Β–Κ―²―Ä–Η–Κ–Α –±–Β–Ζ–Ω–Μ–Α―²–Ϋ–Α, ―²―Ä–Α–Ϋ–Ζ–Η―¹―²–Ψ―Ä–Η –¥–Ψ―Ä–Ψ–≥―•. –ù–Ψ–≤–Η–Ι –Ω―Ä–Η–Ϋ―Ü–Η–Ω –Β–Κ–Ψ–Ϋ–Ψ–Φ―•―½: –Β–Μ–Β–Κ―²―Ä–Η–Κ–Α –¥–Ψ―Ä–Ψ–≥–Α, –Α–Μ–Β ―²―Ä–Α–Ϋ–Ζ–Η―¹―²–Ψ―Ä–Η ¬Ϊ–±–Β–Ζ–Ω–Μ–Α―²–Ϋ―•¬Μ.

βÜë Asanovic, Krste et al. (–™―Ä―É–¥–Β–Ϋ―¨ 18, 2006). ¬ΪThe Landscape of Parallel Computing Research: A View from Berkeley¬Μ (PDF). University of California, Berkeley. Technical Report No. UCB/EECS-2006-183. ¬Ϊ–Γ―²–Α―Ä–Η–Ι –Ω―Ä–Η–Ϋ―Ü–Η–Ω –≤–Η―Ä―•―à–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ–±–Μ–Β–Φ: –½–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è ―²–Α–Κ―²–Ψ–≤–Ψ―½ ―΅–Α―¹―²–Ψ―²–Η βÄî –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Η–Ι –Φ–Β―²–Ψ–¥ –Ω–Ψ–Κ―Ä–Α―â–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Ψ―¹―²―•. –ù–Ψ–≤–Η–Ι –Ω―Ä–Η–Ϋ―Ü–Η–Ω: –½–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è –Ω–Α―Ä–Α–Μ–Β–Μ―•–Ζ–Φ―É ―Ü–Β –Ψ―¹–Ϋ–Ψ–≤–Ϋ–Η–Ι –Φ–Β―²–Ψ–¥ –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Ψ―¹―²―• –Ω―Ä–Ψ―Ü–Β―¹–Ψ―Ä–ΑβÄΠ –ù–Α–≤―•―²―¨ –Ω―Ä–Β–¥―¹―²–Α–≤–Ϋ–Η–Κ–Η Intel, –Κ–Ψ–Φ–Ω–Α–Ϋ―•―½, ―â–Ψ –Ζ–Α–Ζ–≤–Η―΅–Α–Ι –Α―¹–Ψ―Ü―•―é―î―²―¨―¹―è –Ζ –Ω–Ψ–Ζ–Η―Ü―•―î―é βÄî βÄû―΅–Η–Φ –±―•–Μ―¨―à–Α ―΅–Α―¹―²–Ψ―²–Α ―²–Η–Φ –Κ―Ä–Α―â–ΒβÄ€, –Ω–Ψ–Ω–Β―Ä–Β–¥–Ε―É―é―²―¨, ―â–Ψ ―²―Ä–Α–¥–Η―Ü―•–Ι–Ϋ―• –Ω―•–¥―Ö–Ψ–¥–Η –¥–Ψ –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è –Ω―Ä–Ψ–¥―É–Κ―²–Η–≤–Ϋ–Ψ―¹―²―• ―΅–Β―Ä–Β–Ζ –Ζ–±―•–Μ―¨―à–Β–Ϋ–Ϋ―è ―²–Α–Κ―²–Ψ–≤–Ψ―½ ―΅–Α―¹―²–Ψ―²–Η –¥–Ψ―¹―è–≥–Μ–Η ―¹–≤–Ψ―î―½ –Φ–Β–Ε―•.¬Μ

βÜë Patterson, David A. and John L. Hennessy (1998). Computer Organization and Design , Second Edition, Morgan Kaufmann Publishers, p. 715. ISBN 1-55860-428-6 .

βÜë –Α –± Barney, Blaise. Introduction to Parallel Computing . Lawrence Livermore National Laboratory. –ê―Ä―Ö―•–≤ –Ψ―Ä–Η–≥―•–Ϋ–Α–Μ―É –Ζ–Α 29 ―΅–Β―Ä–≤–Ϋ―è 2013. –ü―Ä–Ψ―Ü–Η―²–Ψ–≤–Α–Ϋ–Ψ 9 –Μ–Η―¹―²–Ψ–Ω–Α–¥–Α 2007 . βÜë Hennessy, John L. and David A. Patterson (2002). Computer Architecture: A Quantitative Approach . 3rd edition, Morgan Kaufmann, p. 43. ISBN 1-55860-724-2 .

βÜë Rabaey, J. M. (1996). Digital Integrated Circuits . Prentice Hall, p. 235. ISBN 0-13-178609-1 .

βÜë Flynn, Laurie J. ¬ΪIntel Halts Development of 2 New Microprocessors¬Μ . The New York Times , May 8, 2004. Retrieved on April 22, 2008.

βÜë Moore, Gordon E. (1965). Cramming more components onto integrated circuits (PDF) . Electronics Magazine –Ψ―Ä–Η–≥―•–Ϋ–Α–Μ―É (PDF) –Ζ–Α 18 –Μ―é―²–Ψ–≥–Ψ 2008. –ü―Ä–Ψ―Ü–Η―²–Ψ–≤–Α–Ϋ–Ψ 11 –Μ–Η―¹―²–Ψ–Ω–Α–¥–Α 2006 . βÜë Amdahl, G. (April 1967) ¬ΪThe validity of the single processor approach to achieving large-scale computing capabilities¬Μ. In Proceedings of AFIPS Spring Joint Computer Conference , Atlantic City, N.J., AFIPS Press, pp. 483-85.

βÜë –Λ―Ä–Β–¥ –ë―Ä―É–Κ―¹ –€―•―³―•―΅–Ϋ–Η–Ι –Μ―é–¥–Η–Ϋ–Ψ-–Φ―•―¹―è―Ü―¨ ISBN 0-201-83595-9 βÜë Reevaluating Amdahl's Law [–ê―Ä―Ö―•–≤–Ψ–≤–Α–Ϋ–Ψ 27 –≤–Β―Ä–Β―¹–Ϋ―è 2007 ―É Wayback Machine .] (1988). Communications of the ACM 31(5), pp. 532-33.βÜë Bernstein, A. J. (October 1966). ¬ΪProgram Analysis for Parallel Processing,' IEEE Trans. on Electronic Computers¬Μ. EC-15, pp. 757-62.

βÜë Roosta, Seyed H. (2000). ¬ΪParallel processing and parallel algorithms: theory and computation¬Μ. Springer, p. 114. ISBN 0-387-98716-9 .

βÜë Lamport, Leslie (September 1979). ¬ΪHow to Make a Multiprocessor Computer That Correctly Executes Multiprocess Programs¬Μ, IEEE Transactions on Computers, C-28,9, pp. 690-91.

βÜë Patterson and Hennessy, p. 748.

βÜë Culler, David E.; Jaswinder Pal Singh and Anoop Gupta (1999). Parallel Computer Architecture βÄî A Hardware/Software Approach . Morgan Kaufmann Publishers, p. 15. ISBN 1-55860-343-3 .

βÜë Culler et al. p. 15.

βÜë Patt, Yale (April 2004). The Microprocessor Ten Years From Now: What Are The Challenges, How Do We Meet Them? [–ê―Ä―Ö―•–≤–Ψ–≤–Α–Ϋ–Ψ 14 –Κ–≤―•―²–Ϋ―è 2008 ―É Wayback Machine .] (wmv). Distinguished Lecturer talk at Carnegie Mellon University . Retrieved on November 7, 2007.

βÜë –Α –± Culler et al. p. 124.

βÜë –Α –± Culler et al. p. 125.

βÜë –Α –± Patterson and Hennessy, p. 713.

βÜë –Α –± Hennessy and Patterson, p. 549.

βÜë Patterson and Hennessy, p. 714.

βÜë What is clustering? Webopedia computer dictionary.βÜë Beowulf definition. [–ê―Ä―Ö―•–≤–Ψ–≤–Α–Ϋ–Ψ 2012-10-10 ―É Wayback Machine .] PC Magazine βÜë Architecture share for 06/2007 [–ê―Ä―Ö―•–≤–Ψ–≤–Α–Ϋ–Ψ 14 –Μ–Η―¹―²–Ψ–Ω–Α–¥–Α 2007 ―É Wayback Machine .] . TOP500 Supercomputing Sites. Clusters make up 74.60 % of the machines on the list. Retrieved on November 7, 2007.βÜë Hennessy and Patterson, p. 537.

βÜë MPP Definition. [–ê―Ä―Ö―•–≤–Ψ–≤–Α–Ϋ–Ψ 2013-05-11 ―É Wayback Machine .] PC Magazine . Retrieved on November 7, 2007.βÜë Kirkpatrick, Scott (31 ―¹―•―΅–Ϋ―è 2003). Rough Times Ahead . Science (–Α–Ϋ–≥–Μ.) . –Δ. 299, ⳕ 5607. ―¹. 668βÄî669. doi :10.1126/science.1081623 . ISSN 0036-8075 . –ü―Ä–Ψ―Ü–Η―²–Ψ–≤–Α–Ϋ–Ψ 20 –≥―Ä―É–¥–Ϋ―è 2024 . βÜë Boggan, Sha'Kia and Daniel M. Pressel (August 2007). GPUs: An Emerging Platform for General-Purpose Computation (PDF). ARL-SR-154, U.S. Army Research Lab. Retrieved on November 7, 2007.

βÜë Patterson and Hennessy, pp. 749βÄ™50: ¬ΪAlthough successful in pushing several technologies useful in later projects, the ILLIAC IV failed as a computer. Costs escalated from the $8 million estimated in 1966 to $31 million by 1972, despite the construction of only a quarter of the planned machine . It was perhaps the most infamous of supercomputers. The project started in 1965 and ran its first real application in 1976.¬Μ