SPARC T4

|

Read other articles:

Dekompresi, pengawapampatan, atau pengawamampatan adalah tekanan udara di dalam kabin berkurang secara tiba-tiba.Artikel ini tidak memiliki referensi atau sumber tepercaya sehingga isinya tidak bisa dipastikan. Tolong bantu perbaiki artikel ini dengan menambahkan referensi yang layak. Tulisan tanpa sumber dapat dipertanyakan dan dihapus sewaktu-waktu.Cari sumber: Dekompresi pesawat – berita · surat kabar · buku · cendekiawan · JSTOR Dekompresi ada...

يفتقر محتوى هذه المقالة إلى الاستشهاد بمصادر. فضلاً، ساهم في تطوير هذه المقالة من خلال إضافة مصادر موثوق بها. أي معلومات غير موثقة يمكن التشكيك بها وإزالتها. (نوفمبر 2019) الدوري النمساوي 1983–84 تفاصيل الموسم الدوري النمساوي النسخة 73 البلد النمسا المنظم اتحاد النمسا ...

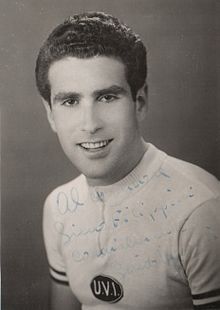

Italian cyclist (1931–2020) Guido MessinaPersonal informationFull nameGuido MessinaBorn(1931-01-04)4 January 1931Monreale, Italy[1]Died10 January 2020(2020-01-10) (aged 89)Caselette, ItalyTeam informationDisciplineTrack, roadRoleRider Medal record Men's cycling: 4000 m pursuit Representing Italy Olympic Games 1952 Helsinki Team World Championships 1948 Amsterdam Ind., amateur 1950 Rocourt Ind., amateur 1951 Milan Ind., amateur 1953 Zürich Ind., amateur 1954 Cologne ...

The wives of Belgian monarchs have all been titled Queen and styled Majesty, with the exception of Leopold III of Belgium's second wife Mary Lilian Baels, who was titled Princess of Belgium and Princess of Réthy. All Belgian monarchs so far have been male, so there have only been female consorts. There have been eight queen consorts of Belgium since 1832. Picture Coat of Arms Name Father Birth Marriage Became Consort Ceased to be Consort Death Spouse Louise-Marie Thérèse Charlotte Isabell...

Genus of birds Myrmotherula Unicolored antwren (Myrmotherula unicolor) Scientific classification Domain: Eukaryota Kingdom: Animalia Phylum: Chordata Class: Aves Order: Passeriformes Family: Thamnophilidae Genus: MyrmotherulaSclater, PL, 1858 Type species Muscicapa pygmaea[1]Gmelin, 1789 Species See text Myrmotherula is a genus of insectivorous passerine birds in the antbird family, Thamnophilidae. These are all small antbirds, measuring 9–11.5 cm (3.5–4.5 in). The genus...

For other uses, see Alashkert (disambiguation). Alashkert Stadium Ալաշկերտ մարզադաշտAlashkert StadiumFormer namesNairi StadiumLocationYerevan, ArmeniaOwnerFC AlashkertCapacity6,850 (1,850 seated)Field size110 x 70 metersSurfacegrassConstructionBuilt1960TenantsAlashkert (2011–present)Noah (2019–2022) Alashkert Stadium (Armenian: Ալաշկերտ մարզադաշտ) is a football stadium in Yerevan, Armenia. It was known as Nairi Stadium until 2013, when it was renamed Alas...

Study of human activity via material culture For other uses, see Archaeology (disambiguation). Not to be confused with Arcology. Excavations at Atapuerca, an archaeological site in Spain. Archaeology or archeology[a] is the study of human activity through the recovery and analysis of material culture. The archaeological record consists of artifacts, architecture, biofacts or ecofacts, sites, and cultural landscapes. Archaeology can be considered both a social science and a branch of t...

Niccolò Gaddi Lambang Kardinal Niccolò Gaddi Niccolò Gaddi (1499–1552) merupakan seorang kardinal Katolik Roma Italia. Biografi Niccolò Gaddi lahir di Firenze pada 1499, sebagai putra dari Taddeo Gaddi dan Antonia Altoviti.[1] Ia merupakan keturunan dari pelukis Abad Pertengahan Taddeo Gaddi.[1] Ia merupakan paman dari Kardinal Taddeo Gaddi dan sedarah dengan Catherine de' Medici.[1] Ia memulai kariernya di Roma sebagai seorang rohaniwan di Kamar Apostolik. Pada ...

King of Getae Dromichaetes - ΔρομιχαίτηςKing of GetaeReignc. 300 – c. 280 BCDiedc. 280 BCBurialSveshtari, BulgariaSpousea daughter of Lysimachus Dromichaetes (Ancient Greek: Δρομιχαίτης, romanized: Dromichaites) was king of the Getae on both sides of the lower Danube (present day Romania and Bulgaria) around 300 BC. Background Thracian helmet with decorations made from bronze and silver. Dated mid-4th century BC. The Getae had been federated in the Odrysian ki...

This article needs additional citations for verification. Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed.Find sources: Effect of taxes and subsidies on price – news · newspapers · books · scholar · JSTOR (July 2016) (Learn how and when to remove this message) Part of a series onTaxation An aspect of fiscal policy Policies Government revenue Property tax equalization Tax revenue...

1961–1970 conflict between Iraq and Kurdish militias First Kurdish–Iraqi WarPart of the Iraqi–Kurdish conflict and the Arab–Israeli conflictDate11 September 1961 – March 1970LocationNorthern IraqResult Stalemate Several Iraqi offensives intended to suppress the Kurdish rebellion fail.[5][6] Iraqi–Kurdish Autonomy Agreement Arabization program continuedBelligerents KDP Supported by: Iran (after 1968) Israel[1] United States (alleged)[2] Bef...

Former Olympic sport Team portable apparatusat the Olympic GamesOverviewSportArtistic gymnasticsGenderWomenYears held1952–1956Reigning championWomen Hungary (HUN) The team portable apparatus was an artistic gymnastics event held at the Summer Olympics. It was only held at the 1952[1] and 1956 Olympic Games.[2] While it is no longer officially contested, it did contain many similarities to modern day rhythmic gymnastics.[3] Medalists Games Gold Silver Bronze...

حضارة نقادة الثانيةمعلومات عامةالبداية 3650 ق.م النهاية 3300 ق.م المنطقة مصر التأثيراتفرع من مصر ما قبل الأسرات الثقافة الأمراتية حضارة نقادة الثالثة تعديل - تعديل مصدري - تعديل ويكي بيانات تشير ثقافة جرزة، التي تسمى أيضًا نقادة الثانية، إلى المرحلة الأثرية في جرزة (أيضًا جيزر...

Japanese manga series Honey and CloverFirst tankōbon volume cover (Shueisha edition), featuring Hagumi Hagu Hanamotoハチミツとクローバー(Hachimitsu to Kurōbā)GenreComing-of-age[1]Romance[2]Slice of life[3] MangaWritten byChica UminoPublished byTakarajimashaShueishaEnglish publisherNA: Viz MediaMagazineCutie Comic (2000–01)Young You (2001–05)Chorus (2005–06)English magazineNA: Shojo BeatDemographicShōjo, joseiOriginal runApril 24, 2000 – ...

Teeradetch MetawarayutNama asalธีรเดช เมธาวรายุทธLahir15 September 1989 (umur 34)Bangkok, ThailandNama lainAlek (หลุยส์)PendidikanUniversitas ChulalongkornPekerjaanPemeranYouTuberTahun aktif2012–sekarangAgenChannel 3 (2013-sekarang)Karya terkenalSapia Jao (2015) Teeradetch Metawarayut (bahasa Thai: ธีรเดช เมธาวรายุทธ; lahir 15 September 1989), nama panggilan Alek (bahasa Thai: อา...

Sequence of operations for a task Algorithms redirects here. For the subfield of computer science, see Analysis of algorithms. For other uses, see Algorithm (disambiguation). This article may require copy editing for grammar, style, cohesion, tone, or spelling. You can assist by editing it. (April 2024) (Learn how and when to remove this message) This article is written like a personal reflection, personal essay, or argumentative essay that states a Wikipedia editor's personal feelings or pre...

1876 Japanese uprising Shinpūren RebellionPart of the Shizoku rebellions of the Meiji periodThe Death in Battle of the Kumamoto Rebels by Tsukioka Yoshitoshi[a]Date24 October 1876 – 25 October 1876LocationKumamoto, Kumamoto Prefecture, JapanResult Government victory Akizuki rebellion and Hagi RebellionBelligerents Meiji Government of Japan Imperial Japanese Army Keishintō Samurai of the Kumamoto DomainCommanders and leaders Kumamoto Garrison: Yasuoka Ryosuke X Taneda Masa...

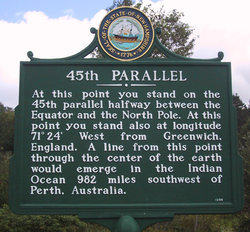

45° 北緯45度線 全ての座標を示した地図 - OSM 全座標を出力 - KML 表示 北緯45度線(ほくい45どせん)は、地球の赤道面より北に地理緯度にして45度の角度を成す緯線である。ヨーロッパ、アジア、太平洋、北アメリカ、大西洋を通過する。 よく北極点から赤道までの距離の中間地点だといわれるが、実際の中間地点は北緯45度線よりも16キロメートル北にある。これは地球�...

Intercollegiate basketball season 2016–17 Wyoming Cowgirls basketballWNIT, Second RoundConferenceMountain West ConferenceRecord22–10 (13–5 Mountain West)Head coachJoe Legerski (14th season)Assistant coaches Gerald Mattinson Bojan Janković Heather Ezell Home arenaArena-AuditoriumSeasons← 2015–162017–18 → 2016–17 Mountain West Conference women's basketball standings vte Conf Overall Team W L PCT W L PCT Colorado State 15 &...

Part of a series of lists aboutHuman anatomy General Features Regions Variations Movements Systems Structures Arteries Bones Eponymous Foramina Glands endocrine exocrine Lymphatic vessels Nerves Organs Systems Veins Muscles Abductors Adductors Depressors Elevators Extensors Flexors Rotators external internal See also Glossary of medicine Epithelia Anatomical terminology Index of anatomy articles Outline of human anatomy Cell types by origin vte In anatomy, extension is a movement of a joint ...