SSE2

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Read other articles:

إيفوي إيفوي مع منتخب غينيا الاستوائية معلومات شخصية الاسم الكامل دانيال بازكيز إيفوي الميلاد 11 مارس 1985 (العمر 39 سنة)مدريد، إسبانيا الطول 1.81 م (5 قدم 11 1⁄2 بوصة) مركز اللعب مدافع، ظهير أيمن، لاعب وسط أيمن الجنسية إسبانيا مسيرة الشباب سنوات فريق 1995–1999 موستولي�...

College basketball team Texas A&M–Corpus Christi Islanders 2023–24 Texas A&M–Corpus Christi Islanders men's basketball team UniversityTexas A&M University–Corpus ChristiHead coachJim Shaw (1st season)ConferenceSouthlandLocationCorpus Christi, TexasArenaAmerican Bank Center (Capacity: 8,500)NicknameIslandersColorsRoyal blue, white, and green[1] NCAA tournament appearances2007, 2022, 2023Conference tournament champions2007,...

† Человек прямоходящий Научная классификация Домен:ЭукариотыЦарство:ЖивотныеПодцарство:ЭуметазоиБез ранга:Двусторонне-симметричныеБез ранга:ВторичноротыеТип:ХордовыеПодтип:ПозвоночныеИнфратип:ЧелюстноротыеНадкласс:ЧетвероногиеКлада:АмниотыКлада:Синапсиды�...

Kotamadya Skjåk di Norwegia memiliki luas 2.079 km² dengan panjang utara-selatan 56,5 km dan jarak timur-barat 65,3 km. Skjåk berpenduduk 2.526 jiwa. Kepadatan penduduk mencapai 1,2 jiwa/km2. Kotamadya ini terletak di fylke Oppland barat laut dan beribu kota di Bismo. Artikel bertopik geografi atau tempat Norwegia ini adalah sebuah rintisan. Anda dapat membantu Wikipedia dengan mengembangkannya.lbs

1987 concert tour by Madonna Who's That Girl World TourTour by MadonnaPromotional poster for the tourLocation Asia North America Europe Associated album True Blue Who's That Girl Start dateJune 14, 1987 (1987-06-14)End dateSeptember 6, 1987 (1987-09-06)Legs3No. of shows38Box officeUS$25 million[a]Madonna concert chronology The Virgin Tour (1985) Who's That Girl World Tour (1987) Blond Ambition World Tour (1990) The Who's That Girl World Tour (billed a...

Pour les articles homonymes, voir BBM. Cet article est une ébauche concernant une localité algérienne. Vous pouvez partager vos connaissances en l’améliorant (comment ?) selon les recommandations des projets correspondants. Bordj Badji Mokhtar Vue de Bordj Badji Mokhtar en 1990 Noms Nom arabe algérien برج باجى مختار Nom amazigh ⴱⵓⵔⴵ ⴱⴰⴵⵉ ⵎⵓⵅⵜⴰⵔ Administration Pays Algérie Wilaya Bordj Badji Mokhtar Code postal 01010 Code ONS 0125 Indicatif...

Pour les articles homonymes, voir Dupont ou Dupond, Du Pont (homonymie) et Nemours (homonymie). DuPont de Nemours Inc. Création 1802 Fondateurs Éleuthère Irénée du Pont de Nemours Forme juridique Société anonyme (NYSE : DD) Action New York Stock Exchange (DD)[1],[2],[3] Slogan The miracles of science Siège social Wilmington (Delaware) États-Unis Direction C. Doyle Président Charles O. Holliday (en) (1999-2009)[4] Activité Chimie - Plastiques - Adhésifs Anciennement ...

Questa voce o sezione sull'argomento anime e manga non cita le fonti necessarie o quelle presenti sono insufficienti. Puoi migliorare questa voce aggiungendo citazioni da fonti attendibili secondo le linee guida sull'uso delle fonti. Segui i suggerimenti del progetto di riferimento. Questa voce o sezione sull'argomento anime e manga non è ancora formattata secondo gli standard. Contribuisci a migliorarla secondo le convenzioni di Wikipedia. Segui i suggerimenti del progetto di rif...

Sceaux 行政国 フランス地域圏 (Région) イル=ド=フランス地域圏県 (département) オー=ド=セーヌ県郡 (arrondissement) アントニー郡小郡 (canton) 小郡庁所在地INSEEコード 92071郵便番号 92330市長(任期) フィリップ・ローラン(2008年-2014年)自治体間連合 (fr) メトロポール・デュ・グラン・パリ人口動態人口 19,679人(2007年)人口密度 5466人/km2住民の呼称 Scéens地理座標 北緯48度4...

この項目には、一部のコンピュータや閲覧ソフトで表示できない文字が含まれています(詳細)。 数字の大字(だいじ)は、漢数字の一種。通常用いる単純な字形の漢数字(小字)の代わりに同じ音の別の漢字を用いるものである。 概要 壱万円日本銀行券(「壱」が大字) 弐千円日本銀行券(「弐」が大字) 漢数字には「一」「二」「三」と続く小字と、「壱」「�...

Belmontcomune Belmont – Veduta LocalizzazioneStato Francia RegioneGrand Est Dipartimento Basso Reno ArrondissementMolsheim CantoneMutzig TerritorioCoordinate48°24′N 7°14′E / 48.4°N 7.233333°E48.4; 7.233333 (Belmont)Coordinate: 48°24′N 7°14′E / 48.4°N 7.233333°E48.4; 7.233333 (Belmont) Superficie10,34 km² Abitanti176[1] (2009) Densità17,02 ab./km² Altre informazioniCod. postale67130 Fuso orarioUTC+1 Codice INSEE670...

Голубянки Самец голубянки икар Научная классификация Домен:ЭукариотыЦарство:ЖивотныеПодцарство:ЭуметазоиБез ранга:Двусторонне-симметричныеБез ранга:ПервичноротыеБез ранга:ЛиняющиеБез ранга:PanarthropodaТип:ЧленистоногиеПодтип:ТрахейнодышащиеНадкласс:ШестиногиеКласс...

此条目序言章节没有充分总结全文内容要点。 (2019年3月21日)请考虑扩充序言,清晰概述条目所有重點。请在条目的讨论页讨论此问题。 哈萨克斯坦總統哈薩克總統旗現任Қасым-Жомарт Кемелұлы Тоқаев卡瑟姆若马尔特·托卡耶夫自2019年3月20日在任任期7年首任努尔苏丹·纳扎尔巴耶夫设立1990年4月24日(哈薩克蘇維埃社會主義共和國總統) 哈萨克斯坦 哈萨克斯坦政府...

Contoh paket garam beriodin yang didistribusikan secara umum. Garam beriodin atau garam beryodium adalah garam meja yang dicampur dengan sejumlah kecil berbagai garam dari unsur iodin. Konsumsi iodin akan mencegah kekurangan iodin. Di seluruh dunia, kekurangan iodin mempengaruhi sekitar dua miliar orang dan merupakan penyebab utama kecacatan intelektual dan perkembangan yang dapat dicegah.[1][2] Kekurangan iodin juga menyebabkan masalah kelenjar tiroid, termasuk gondok endemik...

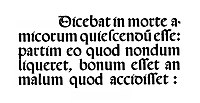

Medieval blackletter script This article needs additional citations for verification. Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed.Find sources: Rotunda script – news · newspapers · books · scholar · JSTOR (April 2013) (Learn how and when to remove this message) Calligraphic writing of the word Rotunda in the Italian script of same name. A 1570s rotunda typeface cut by H...

Florida's NaturalJenisAgricultural cooperativeDidirikan1933 (1933)KantorpusatLake Wales, Florida, United StatesAnggota1100Situs webfloridasnatural.com Florida's Natural Growers adalah perusahaan koperasi pertanian dari Lake Wales, Florida yang hingga saat ini menghimpun 1.100 petani.[1] Perusahaan ini didirikan tahun 1933 sebagai Florida Citrus Canners Cooperative, dan beralih nama menjadi Citrus World tahun 1969 tetapi mengadopsi nama sebelumnya tahun 1998. Perusahaan ini mempro...

Perhimpunan Dokter Hewan IndonesiaSingkatanPDHITanggal pendirian9 Januari 1953; 71 tahun lalu (1953-01-09)TipeOrganisasi profesiKantor pusatGrha Dokter Hewan Jl. Joe Klp. Tiga No.09, RT.7/RW.4, Kebagusan, Kec. Ps. Minggu, Kota Jakarta Selatan, Daerah Khusus Ibukota Jakarta 12520Ketua UmumDr. drh. Muhammad Munawaroh, M.M.Situs webhttps://pdhi.or.id/ Perhimpunan Dokter Hewan Indonesia (disingkat PDHI) adalah organisasi profesi dokter hewan di Indonesia. Ketua Umum Pengurus Besar PDHI saat ...

Fuerza Aérea de Malí Armée de l'air du Mali Emblema de la Fuerzas Armadas de MalíActiva 6 de febrero de 1961-actualidadPaís MalíTipo fuerza aéreaFunción Defensa aéreaParte de Fuerzas armadas de MalíAcuartelamiento BamakoAlto mandoPresidente Assimi GoitaMinistro de Defensa Sadio CamaraComandante General Souleymane DoucouréInsigniasEscarapela Guerras y batallas Guerra de la Franja de AgacherConflicto en el norte de Malí[editar datos en Wikidata] La Fuerza Aérea de Malí (...

2001 extended version of Apocalypse Now directed by Francis Ford Coppola Apocalypse Now ReduxTheatrical release posterDirected byFrancis Ford CoppolaWritten by John Milius Francis Ford Coppola Narration byMichael Herr Produced by Francis Ford Coppola Kim Aubry Starring Marlon Brando Robert Duvall Martin Sheen Frederic Forrest Albert Hall Sam Bottoms Laurence Fishburne Christian Marquand Aurore Clément Harrison Ford Dennis Hopper CinematographyVittorio StoraroEdited by Richard Marks Walter Mu...

此条目页的主題是李翰祥導演之1963年電影。关于梁山伯与祝英台,請見「梁山伯與祝英台 (消歧义)」。 梁山伯與祝英台The Love Eterne基本资料导演李翰祥监制邵逸夫编剧李翰祥主演凌波樂蒂任潔李昆配乐周藍萍摄影賀蘭山戴嘉泰剪辑姜興隆制片商邵氏電影公司片长122 分鐘产地 香港语言華語上映及发行上映日期 英屬香港: 1963年4月4日 (1963-04-04) 臺灣:1963年4月...