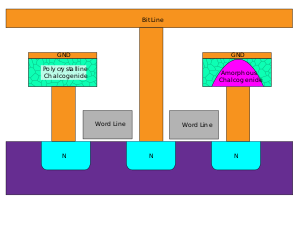

PRAM

|

Read other articles:

This article is about the 2016 Chinese series. For the 2018 Philippine series, see Hindi Ko Kayang Iwan Ka. Chinese TV series or program Stay with MeAlso known asAbandon Me, Hold Me TightGenreRomanceDramaCreated byTong HuaWritten byQian JingjingXu ZiyuanJiang GuangyuDirected byBilly TangRuan WeixinChen GuohuaStarringJoe ChenWang KaiOpening themeStay with Me by Jin ZhiwenEnding themeWhen Love Comes Knocking by Zhang BichenCountry of originChinaOriginal languageMandarinNo. of episodes39Producti...

Peta menunjukkan lokasi Balanga City Data sensus penduduk di Balanga City Tahun Populasi Persentase 199560.912—200071.0883.37%200784.1052.35% Balanga City adalah kota yang terletak di provinsi Bataan, Filipina. Pada tahun 2007, Balanga City memiliki jumlah penduduk sebesar 84.105 jiwa atau 14.065 rumah tangga. Pembagian wilayah Balanga terbagi menjadi 25 barangay, yaitu: Bagong Silang Bagumbayan Cabog-Cabog Camacho (Cadre) Cataning Central Cupang North Cupang Proper Cupang West Dangcol (Ber...

Rudolph W. Giuliani Wali kota New York City 107Masa jabatan1 Januari 1994 – 31 Desember 2001 PendahuluDavid N. DinkinsPenggantiMichael R. Bloomberg Informasi pribadiLahir28 Mei 1944 (umur 79)Brooklyn, New YorkPartai politikRepublikSuami/istriJudith NathanAlma materManhattan CollegeSunting kotak info • L • B Rudolph William Louis Rudy Giuliani, KBE (lahir 28 Mei 1944) adalah politikus, pengacara, dan pengusaha AS dari negara bagian New York. Ia adalah mantan w...

StyxGambar S/2012 P 1 yang ditemukan oleh teleskop hubble (ditunjukkan dengan P5)PenemuanDitemukan olehShowalter, M. R. et al.Tanggal penemuan 26 June 2012 (verified 7 July 2012) Metode deteksiFotografiCiri-ciri orbit[1]Jari-jari orbit rata-rata42,000 km ± 2,000 kmEksentrisitas≈ 0Periode orbit20.2 ± 0.1 hariInklinasi≈ 0Satelit dariPlutoCiri-ciri fisikJari-jari rata-rata5–12.5 km[1] Styx (dikenal juga sebagai S/2012 (134340) 1, S/2012 P 1, atau P5) adalah...

Artikel ini membutuhkan rujukan tambahan agar kualitasnya dapat dipastikan. Mohon bantu kami mengembangkan artikel ini dengan cara menambahkan rujukan ke sumber tepercaya. Pernyataan tak bersumber bisa saja dipertentangkan dan dihapus.Cari sumber: Universitas Mataram – berita · surat kabar · buku · cendekiawan · JSTOR Universitas MataramLogo Universitas MataramMotoLembaga yang mendunia. (Institution Wide Word)JenisPerguruan Tinggi NegeriDidirikan01 Okt...

Disambiguazione – Se stai cercando altri significati, vedi Serie A 1983-1984 (disambigua). Serie A 1983-1984 Competizione Serie A Sport Calcio Edizione 82ª (52ª di Serie A) Organizzatore Lega Nazionale Professionisti Date dall'11 settembre 1983al 13 maggio 1984 Luogo Italia Partecipanti 16 Formula girone unico Risultati Vincitore Juventus(21º titolo) Retrocessioni GenoaPisaCatania Statistiche Miglior marcatore Michel Platini (20) Incontri disputati 240 Gol segnati 57...

Cet article possède un paronyme, voir Claquette. Si ce bandeau n'est plus pertinent, retirez-le. Cliquez ici pour en savoir plus. Cet article ne s'appuie pas, ou pas assez, sur des sources secondaires ou tertiaires (décembre 2019). Pour améliorer la vérifiabilité de l'article ainsi que son intérêt encyclopédique, il est nécessaire, quand des sources primaires sont citées, de les associer à des analyses faites par des sources secondaires. Si ce bandeau n'est plus pertinent, retirez...

Men's 110 metres hurdles at the 2023 World ChampionshipsGrant Holloway competing in the heats.VenueNational Athletics CentreDates20 August (heats)21 August (semi-final & final)Competitors45 from 28 nationsWinning time12.96Medalists Grant Holloway United States Hansle Parchment Jamaica Daniel Roberts United States← 20222025 → Video on YouTubeOfficial Video Events at the2023 World Championshi...

Ancient Egyptian culture from the late 4th millennium BC This article is about the third millennium BC Nubian culture. For the type of mathematical group, see A-group. The Relief of Gebel Sheikh Suleiman likely shows the victory of an early Pharaoh, possibly Djer, over A-Group Nubians circa 3000 BC, nearly dating back to the First Dynasty. This rock carving represents an Egyptian campaign into Nubia and was found near the second cataract of the Nile River. ChalcolithicEneolithic, Aeneolithic,...

Brazilian footballer This biography of a living person needs additional citations for verification. Please help by adding reliable sources. Contentious material about living persons that is unsourced or poorly sourced must be removed immediately from the article and its talk page, especially if potentially libelous.Find sources: Ilan footballer – news · newspapers · books · scholar · JSTOR (January 2010) (Learn how and when to remove this message)...

保良局馬錦明夫人章馥仙中學Po Leung Kuk Mrs.Ma-Cheung Fook Sien College翻漆後的校舍東北面(2022年3月)地址 香港新界離島區大嶼山東涌富東邨类型津貼中學宗教背景無隶属保良局创办日期1997年学区香港離島區東涌校長柯玉琼女士副校长鄭健華先生,劉俊偉先生助理校长梁煥儀女士职员人数56人年级中一至中六学生人数約700人,24個班別校訓愛、敬、勤、誠校歌保良局屬下校歌�...

British-American astrophysicist For the American politician, see Joseph Silk (politician). Joseph SilkSilk in 2015Born (1942-12-03) 3 December 1942 (age 81)London, EnglandCitizenshipUKUnited States[citation needed]Alma materClare College, CambridgeHarvard UniversityAwardsRoyal Society Bakerian Medal (2007)Balzan Prize (2011)Gruber Prize in Cosmology (2019)Scientific careerFieldsCosmologyInstitutionsInstitut d'astrophysique de ParisUniversity of OxfordUniversity of California...

هذه المقالة عن المجموعة العرقية الأتراك وليس عن من يحملون جنسية الجمهورية التركية أتراكTürkler (بالتركية) التعداد الكليالتعداد 70~83 مليون نسمةمناطق الوجود المميزةالبلد القائمة ... تركياألمانياسورياالعراقبلغارياالولايات المتحدةفرنساالمملكة المتحدةهولنداالنمساأسترالي�...

土库曼斯坦总统土库曼斯坦国徽土库曼斯坦总统旗現任谢尔达尔·别尔德穆哈梅多夫自2022年3月19日官邸阿什哈巴德总统府(Oguzkhan Presidential Palace)機關所在地阿什哈巴德任命者直接选举任期7年,可连选连任首任萨帕尔穆拉特·尼亚佐夫设立1991年10月27日 土库曼斯坦土库曼斯坦政府与政治 国家政府 土库曼斯坦宪法 国旗 国徽 国歌 立法機關(英语:National Council of Turkmenistan) ...

Citra satelit yang menunjukkan pergerakan hurricane mendekati pantai timur Amerika Serikat. Bagian dari seri alamCuaca Musim kalender Dingin Semi Panas Gugur Musim tropis Kemarau Harmattan Hujan Badai Awan Awan kumulonimbus Awan arcus Angin kencang Microburst Heat burst Derecho Petir Badai petir Badai petir massa udara Salju petir Badai petir kering Mesosiklon Supercell Tornado Tornado antisiklon Landspout Sengkayan Puting beliung Pusaran api Antisiklon Siklon Tekanan rendah kutub Siklon ekst...

اقتُرح دمج محتويات هذه المقالة مع المعلومات الموجودة في جزيرة أسينشين. (ناقش) كنيسة سانت ماري في جورجتاون. المسيحية هي الديانة السائدة في جزيرة أسينشين، حيث أن 100% من السكان الجزيرة البالغ عددهم 880 نسمة يعتنقون الديانة المسيحية والغالبيَّة العظمى منهم من أصول أوروبيَّة.[1&...

Katedral San MarinoKatedral-Basilika Santo Marinusbahasa Italia: Basilica di San MarinoKatedral San MarinoLokasiKota San MarinoNegaraSan MarinoDenominasiGereja Katolik RomaArsitekturStatusKatedral, Basilika minorStatus fungsionalAktifAdministrasiKeuskupanKeuskupan San Marino-Montefeltro Katedral San Marino yang bernama resmi Katedral-Basilika Santo Marinus (bahasa Italia: Basilica di San Marino) adalah sebuah gereja kon-katedral dan basilika Katolik yang terletak di Kota San Marino, i...

Railway line in China This article uses bare URLs, which are uninformative and vulnerable to link rot. Please consider converting them to full citations to ensure the article remains verifiable and maintains a consistent citation style. Several templates and tools are available to assist in formatting, such as reFill (documentation) and Citation bot (documentation). (August 2022) (Learn how and when to remove this message) This article needs additional citations for verification. Please help ...

Irish College of OphthalmologistsMottoEye doctors of Ireland, protecting your visionTypePrivateEstablished1991Students195Address121 St. Stephen's Green, Dublin, IrelandCampusUrbanDeanPresidentCEOYvonne DelaneyAlison BlakeSiobhán KellyAffiliationsRCSIWebsitehttp://www.eyedoctors.ie The Irish College of Ophthalmologists or ICO is the recognised body for ophthalmology training in Ireland. Founded in 1991, it represents over 200 ophthalmologists in Ireland.[1] Its current president is D...

Village in Faiyum Governorate, Egypt This article is about the archaeological site in Egypt. For the Palestinian town in the West Bank, see Huwara. For the town in northern Jordan, see Huwwarah. For the ancient town in southern Jordan, see Humeima. For the Berber tribe, see Hawwara. Limestone pyramid. Sir Flinders Petrie thought that this represented a model for Hawara pyramid. 12th Dynasty. From Hawara, Egypt. The Petrie Museum of Egyptian Archaeology, London Petrie unearthed a number of viv...