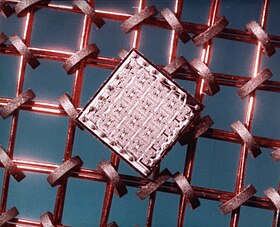

DRAM

|

Read other articles:

Luca Rossettini Informasi pribadiTanggal lahir 9 Mei 1985 (umur 38)Tempat lahir Padua, ItaliaTinggi 1,87 m (6 ft 1+1⁄2 in)Posisi bermain BekInformasi klubKlub saat ini CagliariNomor 15Karier junior PadovaKarier senior*Tahun Tim Tampil (Gol)2004–2007 Padova 44 (3)2007–2012 Siena 108 (1)2012– Cagliari 0 (0) * Penampilan dan gol di klub senior hanya dihitung dari liga domestik dan akurat per 23 Mei 2012 Luca Rossettini (lahir 9 Mei 1985) adalah seorang pemai...

Pour les articles homonymes, voir Jacques Roux et Roux. Jacques RouxVue d'artiste de Jacques Roux rédigeant le compte rendu de l'exécution de Louis XVI, le 21 janvier 1793. Détail d'une gravure de J.-Frédéric Cazenave d'après Charles Benazech, BnF, 1795.BiographieNaissance 21 août 1752Pranzac (Royaume de France)Décès 10 février 1794 (à 41 ans)Bicêtre (République française)Sépulture Cimetière de GentillyNationalité FranceActivités Homme politique, prêtre catholiq...

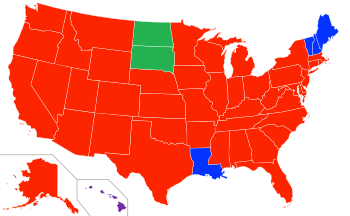

اللغات (2007) [1] الإنجليزية (فقط) 225.5 مليون الإسبانية بما فيها الكريولية 34.5 مليون الصينية 2.5 مليون الفرنسية بما فيها الكريولية 2 مليون التغالوغية 1.5 مليون الفيتنامية 1.2 مليون الألمانية 1.1 مليون الكورية 1.1 مليون اللغة الإنجليزية هي اللغة الوطنية بحكم الأمر الواقع في الولايا�...

Artikel ini sebatang kara, artinya tidak ada artikel lain yang memiliki pranala balik ke halaman ini.Bantulah menambah pranala ke artikel ini dari artikel yang berhubungan atau coba peralatan pencari pranala.Tag ini diberikan pada Maret 2016. SMA Negeri 1 BondowosoInformasiJurusan atau peminatanIPA dan IPSRentang kelasX, XI IPA, XI IPS, XII IPA, XII IPSKurikulumKurikulum Tingkat Satuan PendidikanAlamatLokasiJl. Curahdami, Bondowoso, Jawa TimurMoto SMA Negeri (SMAN) 1 Bondowoso, merupakan sala...

2015 single by Martin JensenSíSingle by Martin JensenReleased20 March 2015 (2015-03-20)Recorded2014GenreDance[1]pop[2]Length2:58LabelDisco:waxMartin Jensen singles chronology Sí (2015) Night After Night (2015) Sí is the debut single by Danish DJ and producer Martin Jensen. It was released on 20 March 2015 as digital download by Disco:wax. The song has peaked to number 55 on the Swedish Singles Chart. The song is a remix of a Cristiano Ronaldo celebration at t...

Curug Jenggala Curug Jenggala adalah air terjun yang berlokasi di Ketenger, Baturaden, Banyumas. Air terjun ini memiliki ketinggian 30 meter dari permukaan tanah.[1] Curug ini mempunyai tiga air terjun yang tingginya sejajar, dengan air terjun yang di tengah memiliki arus yang paling deras. Objek wisata ini menampilkan keindahan alam yang masih asli dan air terjun yang memesona. Di bawah air terjun terdapat sungai dengan batuan besar. Lokasinya berada di Dusun Kalipagu, Ketenger, Batu...

Bandar Udara Kiev beralih ke halaman ini. Untuk kegunaan lain, lihat Bandar Udara Kiev (disambiguasi). Untuk Bandar Udara Zhuliany, lihat Bandar Udara Internasional Zhuliany Kiev. Artikel ini memerlukan pemutakhiran informasi. Harap perbarui artikel dengan menambahkan informasi terbaru yang tersedia. Bandar Udara Internasional BoryspilМіжнародний аеропорт БориспільIATA: KBPICAO: UKBBInformasiJenisPublik/MiliterPengelolaPemerintah SipilMelayaniKyiv, UkrainaLokasiBor...

Voce principale: Kickers Emden. Kickers EmdenStagione 2008-2009Sport calcio Squadra Kickers Emden Allenatore Stefan Emmerling (1ª-31ª) Thomas Richter (32ª-38ª) 3. Liga6º posto Maggiori presenzeCampionato: Zedi, Masuch, Pfingsten-Reddig, Ramaj, Hammouchi (37)Totale: Zedi, Masuch, Pfingsten-Reddig, Ramaj, Hammouchi (37) Miglior marcatoreCampionato: Neitzel (11)Totale: Neitzel (11) StadioEmbdena-Stadion Maggior numero di spettatori6 000 vs. Fortuna Düsseldorf Minor numero di spe...

Questa voce sull'argomento calciatori italiani è solo un abbozzo. Contribuisci a migliorarla secondo le convenzioni di Wikipedia. Segui i suggerimenti del progetto di riferimento. Mario Dal Molin Nazionalità Italia Calcio Ruolo Centrocampista Termine carriera 1968 CarrieraGiovanili 19??-1957 MarosticenseSquadre di club1 1957-1958 Marosticense? (?)1958-1960 Marzotto Valdagno34 (1)1960-1961 Palermo18 (2)1961-1963 Simmenthal-Monza25 (3)1963-1964 Marzot...

Zirah dan senjata dari Eropa. Polisi anti huru-hara di Washington D.C., Amerika Serikat mengenakan pakaian perlindungan yang merupakan tipe zirah masa modern. Zirah (bahasa Inggris: Body armor) adalah pakaian atau lapisan pelindung yang dikenakan untuk melindungi tubuh maupun kendaraan dari senjata atau benda yang dapat memberi luka fisik. Istilah zirah identik dengan pakaian perlindungan untuk berperang pada zaman dahulu, meskipun pada masa modern polisi dan tentara juga menggunakan zirah ya...

Dario Martin Nazionalità Italia Calcio Ruolo Centrocampista Termine carriera 1937 CarrieraSquadre di club1 1920-1934 Torino250 (34)1934-1937 Pinerolo? (?)Nazionale 1927-1930 Italia2 (0) 1 I due numeri indicano le presenze e le reti segnate, per le sole partite di campionato.Il simbolo → indica un trasferimento in prestito. Modifica dati su Wikidata · Manuale Dario Martin (Pinerolo, 19 gennaio 1903 – Pinerolo, 20 giugno 1952) è stato un calciatore italiano, ...

Daily English events related to the pandemic in 2022 Part of a series on theCOVID-19 pandemicin the United Kingdom, British Overseas Territories and Crown Dependencies History Responses Legislation Statistics (Part of the global COVID-19 pandemic) Locations London Countries England Scotland Wales Northern Ireland Crown Dependencies Guernsey Isle of Man Jersey British Overseas Territories Anguilla Akrotiri and Dhekelia Bermuda British Indian Ocean Territory British Virgin Islands Cayman Island...

River in Western Canada South Saskatchewan RiverThe University Bridge over the South Saskatchewan River at SaskatoonThe South Saskatchewan River drainage basinThe mouth in SaskatchewanShow map of SaskatchewanSouth Saskatchewan River (Canada)Show map of CanadaLocationCountryCanadaProvincesAlbertaSaskatchewanPhysical characteristicsSource confluenceOldman and Bow Rivers • locationMunicipal District of Taber, Alberta • coordinates49°56′00″N 111°41′30�...

American merchant and philanthropist For his son, the anti-slavery activist, see Amos A. Lawrence. For the football player, see Amos Lawrence (American football). This article includes a list of general references, but it lacks sufficient corresponding inline citations. Please help to improve this article by introducing more precise citations. (October 2014) (Learn how and when to remove this message) Amos LawrenceBorn(1786-04-22)April 22, 1786Groton, Massachusetts, U.S.DiedDecember 31, 1852(...

В Википедии есть статьи о других людях с фамилией Стивен. Лесли Стивен Дата рождения 28 ноября 1832(1832-11-28)[1][2][…] Место рождения Лондон, Великобритания Дата смерти 22 февраля 1904(1904-02-22)[1][2][…] (71 год) Место смерти Кенсингтон Гражданство (подданство) Великобри...

Ponte alla CarraiaLocalizzazioneStato Italia CittàFirenze AttraversaArno Coordinate43°46′12.87″N 11°14′50.09″E43°46′12.87″N, 11°14′50.09″E Dati tecniciTipoPonte ad arco Materialelegno e pietra Campate5 Lunghezza140 m Larghezza14 m RealizzazioneProgettistaEttore Fagiuoli Costruzione1218-1948 (ricostruzione) Inaugurazione1952 e 1948 CostruttoreEttore Fagiuoli Intitolato acarro Mappa di localizzazione Modifica dati su Wikidata · Manuale Il ponte alla Carraia, dett...

Nigerian-American basketball player Warith AlatisheAlatishe with Oregon State in 2021No. 8 – Texas LegendsPositionSmall forwardLeagueNBA G LeaguePersonal informationBorn (2000-01-22) January 22, 2000 (age 24)Ibadan, NigeriaNationalityNigerian / AmericanListed height6 ft 8 in (2.03 m)Listed weight210 lb (95 kg)Career informationHigh schoolWestside (Houston, Texas)College Nicholls (2018–2020) Oregon State (2020–2022) NBA draft2023: undraftedPlaying ca...

Untuk kegunaan lain, lihat Translasi (disambiguasi).Translasi mRNA Translasi dalam genetika dan biologi molekular adalah proses penerjemahan urutan nukleotida yang ada pada molekul mRNA menjadi rangkaian asam-asam amino yang menyusun suatu polipeptida atau protein.[1] Transkripsi dan Translasi merupakan dua proses utama yang menghubungkan gen ke protein.[2] Translasi hanya terjadi pada molekul mRNA, sedangkan rRNA dan tRNA tidak ditranslasi.[1] Molekul mRNA yang merupa...

Medical university located in Stockholm, Sweden Karolinska InstituteKarolinska InstitutetFormer namesKongl. Carolinska Medico Chirurgiska Institutet (1817–1968)MottoAtt förbättra människors hälsa (Swedish)Motto in EnglishTo improve human healthTypePublicEstablished1810; 214 years ago (1810)Endowment576,1 million EUR (2010)BudgetSEK 6.67 billion[1]Vice-ChancellorAnnika Östman WernersonAdministrative staff4,820 (2016)[1]Students6,481 (FTE, 2020)[...

Global diabetes charity T1InternationalFormation2014HeadquartersLondon, UKFounderElizabeth PfiesterWebsitewww.t1international.com T1International is a not for profit organization that advocates for people with type 1 diabetes.[1] It launched the insulin4all social media campaign and organised two high profile protests outside Ely Lilly and Company headquarters.[2] History T1International was founded by Elizabeth Pfiester in 2014.[3][4] The group has a focus on ...