Transport triggered architecture

|

Read other articles:

Josef Nae Soi Wakil Gubernur Nusa Tenggara Timur ke-9Masa jabatan5 September 2018 – 5 September 2023PresidenJoko WidodoGubernurViktor Laiskodat PendahuluBenny Alexander LitelnoniPenggantiPetahanaAnggota DPR RI Fraksi GolkarMasa jabatan1 Oktober 2004 – 26 Februari 2018PresidenMegawati SoekarnoputriSusilo Bambang YudhoyonoJoko Widodo Informasi pribadiLahir22 September 1953 (umur 70)Mataloko, NgadaPartai politikGolkarAnak2Alma materUniversitas Atma Jaya JakartaPeke...

Masmimar MangiangLahir(1949-09-10)10 September 1949Limbanang, Suliki, Lima Puluh Kota, Sumatera BaratMeninggal29 Juni 2020(2020-06-29) (umur 70)JakartaKebangsaanIndonesiaPekerjaanWartawan, pengajarDikenal atasAhli bahasa mediaOrang tuaM. Sain Dt. Manggung Mangiang (ayah) Sitti Rugaiyah (ibu) Masmimar Mangiang (10 September 1949 – 29 Juni 2020)[1] adalah seorang wartawan dan pakar bahasa jurnalistik Indonesia. Ia juga merupakan pengajar di Departemen Komunikasi FI...

Style of Jewish music For the 2015 war-drama film, see Klezmer (film). KlezmerNative nameקלעזמערOther namesJewish instrumental folk music, Freylekh musicStylistic originsOld European dance musicreligious Jewish musicRomanian musicMoldovan musicUkrainian musicPolish musicBaroque musicOttoman musicGreek musicCultural originsAshkenazic Jewish ceremonies, especially weddings, in Eastern EuropeTypical instrumentsStandard orchestra instruments, accordion, cimbalom Menorah(מְנוֹרָה) F...

2017 Indian Hindi web series Bewafaa sii WafaaCover photoGenreRomance Suspense DramaCreated bySOL ProductionsDeveloped byEkta KapoorWritten byStory and ScreenplayVibha SinghDialoguesEisha ChopraDirected bySonam NairRanjan SinghCreative directorNimisha PandeyStarringSamir SoniAditi VasudevDipannita SharmaTheme music composerAmit TrivediOpening themeBewafaa sii Wafaa, Ishq Ne Di SazaaComposersBackground MusicAashish RegoCountry of originIndiaOriginal languagesHindiEnglishNo. of seasons1No. of e...

2012 studio album by Alicia KeysGirl on FireStudio album by Alicia KeysReleasedNovember 22, 2012 (2012-11-22)Recorded2011–2012Studio Jungle City Oven (New York City) Geejam (Port Antonio) Chalice Record Plant (Los Angeles) Metropolis (London) GenreR&BLength53:08LabelRCAProducer Alicia Keys Babyface Jeff Bhasker Antonio Dixon Dr. Dre Rodney Jerkins Malay Pop & Oak Salaam Remi Jamie Smith Swizz Beatz Alicia Keys chronology The Element of Freedom(2009) Girl on F...

Disambiguazione – Se stai cercando l'omonimo ciclista spagnolo, vedi Carlos Rodríguez Cano. Questa voce sull'argomento schermidori venezuelani è solo un abbozzo. Contribuisci a migliorarla secondo le convenzioni di Wikipedia. Carlos Rodríguez Nazionalità Venezuela Altezza 170 cm Peso 69 kg Scherma Specialità Fioretto Palmarès Competizione Ori Argenti Bronzi Giochi Panamericani 0 0 4 Per maggiori dettagli vedi qui Statistiche aggiornate al 25 giugno 2009 Modifica dati s...

Archaeological site in Croatia Krapina Neanderthal siteHušnjakovo brdo (Croatian)Hušnjakovo Hill finding siteShown within Krapina-Zagorje CountyShow map of Krapina-Zagorje CountyKrapina Neanderthal site (Croatia)Show map of CroatiaKrapina Neanderthal site (Europe)Show map of EuropeLocationWestern part of KrapinaRegionKrapina-Zagorje County, CroatiaCoordinates46°9′53″N 15°51′49″E / 46.16472°N 15.86361°E / 46.16472; 15.86361HistoryPeriodsPalaeolithicCu...

Malaysian politician and lawyer This biography of a living person needs additional citations for verification. Please help by adding reliable sources. Contentious material about living persons that is unsourced or poorly sourced must be removed immediately from the article and its talk page, especially if potentially libelous.Find sources: Alan Ling – news · newspapers · books · scholar · JSTOR (December 2015) (Learn how and when to remove this message...

Kejuaraan DuniaFormula Satu FIA 1994 Juara Dunia Pembalap: Michael Schumacher Juara Dunia Konstruktor: Williams-Renault Sebelum: 1993 Sesudah: 1995 Balapan menurut negaraBalapan menurut musimSeri pendukung: Piala Super Porsche Michael Schumacher (foto tahun 2012) keluar sebagai juara dunia pembalap F1 musim 1994. Damon Hill (foto tahun 1995) menjadi runner-up dengan satu poin, dengan membalap untuk tim Williams. Gerhard Berger (foto tahun 1991) dari tim Scuderia Ferrari menyelesaikan musim i...

この項目には、一部のコンピュータや閲覧ソフトで表示できない文字が含まれています(詳細)。 数字の大字(だいじ)は、漢数字の一種。通常用いる単純な字形の漢数字(小字)の代わりに同じ音の別の漢字を用いるものである。 概要 壱万円日本銀行券(「壱」が大字) 弐千円日本銀行券(「弐」が大字) 漢数字には「一」「二」「三」と続く小字と、「壱」「�...

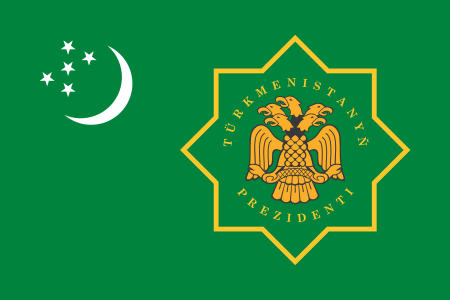

土库曼斯坦总统土库曼斯坦国徽土库曼斯坦总统旗現任谢尔达尔·别尔德穆哈梅多夫自2022年3月19日官邸阿什哈巴德总统府(Oguzkhan Presidential Palace)機關所在地阿什哈巴德任命者直接选举任期7年,可连选连任首任萨帕尔穆拉特·尼亚佐夫设立1991年10月27日 土库曼斯坦土库曼斯坦政府与政治 国家政府 土库曼斯坦宪法 国旗 国徽 国歌 立法機關(英语:National Council of Turkmenistan) ...

2020年夏季奥林匹克运动会波兰代表團波兰国旗IOC編碼POLNOC波蘭奧林匹克委員會網站olimpijski.pl(英文)(波兰文)2020年夏季奥林匹克运动会(東京)2021年7月23日至8月8日(受2019冠状病毒病疫情影响推迟,但仍保留原定名称)運動員206參賽項目24个大项旗手开幕式:帕维尔·科热尼奥夫斯基(游泳)和马娅·沃什乔夫斯卡(自行车)[1]闭幕式:卡罗利娜·纳亚(皮划艇)&#...

Indian Institute of Millets Researchभारतीय कदन्न अनुसंधान संस्थानTypeUnder aegis of ICAREstablished1958AffiliationICARLocationHyderabad, Telangana, IndiaWebsitemillets.res.in The Indian Institute of Millets Research (ICAR-IIMR) located at Rajendranagar (Hyderabad, Telangana, India) is an agricultural research institute engaged in basic and strategic research on sorghum and other millets. IIMR operates under the aegis of Indian Council of Agr...

Baseball team in Waldorf, Maryland, US Southern Maryland Blue Crabs Team logo Cap insignia InformationLeagueAtlantic League of Professional Baseball (South Division)LocationWaldorf, MarylandBallparkRegency Furniture StadiumFounded2006Division championships3 (2009, 2012, 2013)ColorsNavy blue, light blue, red, tan, white MascotPinch the CrabRetired numbers42OwnershipCrabs on Deck, LLCManagerStan CliburnGeneral ManagerCourtney KnichelWebsitesomdbluecrabs.com...

For the thoroughbred racehorse, see Petrarch (horse). For his namesake crater on Mercury, see Petrarch (crater). 14th-century Italian scholar and poet Francis PetrarchPortrait by Altichiero, c. 1370–1380BornFrancesco di Petracco(1304-07-20)20 July 1304Comune of ArezzoDied19 July 1374(1374-07-19) (aged 69)Arquà, PaduaResting placeArquà PetrarcaOccupationScholarpoetCatholic clericLanguageItalian (Tuscan dialect)LatinNationalityAretineEducationUniversity of MontpellierUniversity o...

Oil spill in the Gulf of Mexico This article is about the oil spill itself. For the initial explosion, see Deepwater Horizon explosion. For other related articles, see Deepwater Horizon (disambiguation). Deepwater Horizon oil spillAs seen from space by the Terra satellite on 24 May 2010LocationMacondo Prospect (Mississippi Canyon Block 252), in the North-central Gulf of Mexico, United States (south of Louisiana)Coordinates28°44′17″N 88°21′58″W / 28.73806°N 88.36611�...

City in Central, ParaguayFernando de la MoraCityFernando de la Mora FlagFernando de la MoraLocation in ParaguayCoordinates: 25°19′12″S 57°32′24″W / 25.32000°S 57.54000°W / -25.32000; -57.54000Country ParaguayDepartmentCentralFoundedFebruary 28, 1939Government • Intendente MunicipalAlcides Ramón Riveros Candia (PLRA)Area • Total21 km2 (8 sq mi)Elevation143 m (469 ft)Population • Total183,390&...

Artikel ini bukan mengenai [[:orang Oroch dari Khabarovsk Krai, atau orang Oroqen dari Tiongkok]]. OroksNama alternatif:Orok, Ul'ta, Ulcha, Uil'ta, NaniGrup orang UiltaDaerah dengan populasi signifikan Rusia295[1] Jepang20BahasaOrok, Rusia, JepangAgamaShamanisme, Kristen Ortodoks RusiaKelompok etnik terkaitAinu, Nivkh, Itelmen, Even, Koryak, Evenk, Ulch, Nanai, Oroch, Udege Orok (Ороки dalam bahasa Rusia; penyebutan diri: Ulta, Ulcha), yang terkadang disebut Uilta, adal...

NegrosLokasi NegrosGeografiLokasiAsia TenggaraKepulauanVisayasLuas13.328 km2Peringkat luas62Titik tertinggiKanlaon (2.435 m)PemerintahanNegaraFilipinaProvinsiNegros Occidental, Negros OrientalKota terbesarBacolod (429.076 jiwa)KependudukanPenduduk3.700.000 jiwa (2000)Kepadatan283 jiwa/km2Kelompok etnikVisayas Negros adalah pulau yang terletak di kepulauan Visayas, Filipina, di 10°N 123°E / 10°N 123°E / 10; 123. Pulau ini a...

LOSC LilleSaison 2016-2017 Généralités Couleurs Blanc, bleu et rouge Stade Stade Pierre-Mauroy50 157 places Président Michel Seydouxpuis Gérard Lopez Entraîneur Frédéric Antonettipuis Patrick Collotpuis Franck Passi Résultats Championnat Onzième 46 points (13V, 7N, 18D)(40 buts pour, 47 buts contre) Coupe de France Quarts de finaleÉliminé par l'AS Monaco (2-1) Coupe de la Ligue Huitièmes de finaleÉliminé par le Paris Saint-Germain (3-1) Ligue Europa 3e tour de qualif...