![]() –ö–æ–Ω—Å–æ–ª—å –æ–ø–µ—Ä–∞—Ç–æ—Ä–∞ IBM 7030 –£ –ú—É–∑–µ—ó –ú–∏—Å—Ç–µ—Ü—Ç–≤ —ñ –¢–æ—Ä–≥—ñ–≤–ª—ñ, –ü–∞—Ä–∏–∂

–ö–æ–Ω—Å–æ–ª—å –æ–ø–µ—Ä–∞—Ç–æ—Ä–∞ IBM 7030 –£ –ú—É–∑–µ—ó –ú–∏—Å—Ç–µ—Ü—Ç–≤ —ñ –¢–æ—Ä–≥—ñ–≤–ª—ñ, –ü–∞—Ä–∏–∂

IBM 7030, також відомий як Stretch — перший суперкомп'ютер компанії IBM, побудований на транзисторах. Був найшвидшою ЕОМ у світі з 1961 до 1964 року, коли запрацювала перша машина CDC 6600.[1][2]

Машину було спроектовано під потреби, сформульовані Едвардом Теллером з Ліверморської національної лабораторії; перший екземпляр було поставлено Лос-Аламоській національній лабораторії у 1961-му, а другий — у вигляді зміненої версії, що отримала назву IBM 7950 Harvest — Агентству національної безпеки у 1962-му. У атомному центрі Алдермастон (Велика Британія) комп'ютер інтенсивно використовувався для досліджень, після того, як було розроблено компілятор з Фортрана «S2» з підтримкою динамічних масивів.[3][4]

–ó–±—É–¥–æ–≤–∞–Ω—ñ IBM 7030 –≤–∏–π—à–ª–∏ –∑–Ω–∞—á–Ω–æ –ø–æ–≤—ñ–ª—å–Ω—ñ—à–∏–º–∏, –Ω—ñ–∂ –æ—á—ñ–∫—É–≤–∞–ª–æ—Å—è, —ñ —Ç–∞–∫ —ñ –Ω–µ –∑–º–æ–≥–ª–∏ –¥–æ—Å—è–≥–Ω—É—Ç–∏ –∑–∞–ø–ª–∞–Ω–æ–≤–∞–Ω–∏—Ö –ø–æ–∫–∞–∑–Ω–∏–∫—ñ–≤ —à–≤–∏–¥–∫–æ–¥—ñ—ó (–¥–æ—Å–∏—Ç—å –∞–≥—Ä–µ—Å–∏–≤–Ω–∏—Ö –¥–ª—è —á–∞—Å—É). –ö–æ–º–ø–∞–Ω—ñ—è IBM –±—É–ª–∞ –∑–º—É—à–µ–Ω–∞ –∑–Ω–∏–∑–∏—Ç–∏ —Ü—ñ–Ω—É –∑ 13,5 –º—ñ–ª—å–π–æ–Ω—ñ–≤ –¥–æ–ª–∞—Ä—ñ–≤ –°–®–ê –¥–æ 7,78 –º—ñ–ª—å–π–æ–Ω—ñ–≤, —ñ –ø—Ä–∏–ø–∏–Ω–∏—Ç–∏ –ø—Ä–æ–¥–∞–∂ –º–∞—à–∏–Ω–∏ (–∫—Ä—ñ–º –∑–∞–º–æ–≤–Ω–∏–∫—ñ–≤, —â–æ –≤–∂–µ –ø—ñ–¥–ø–∏—Å–∞–ª–∏ –∫–æ–Ω—Ç—Ä–∞–∫—Ç–∏). –ñ—É—Ä–Ω–∞–ª PC World –Ω–∞–∑–≤–∞–≤ IBM Stretch –æ–¥–Ω—ñ—î—é –∑ –Ω–∞–π–±—ñ–ª—å—à–∏—Ö –Ω–µ–≤–¥–∞—á –ø—Ä–æ–µ–∫—Ç-–º–µ–Ω–µ–¥–∂–º–µ–Ω—Ç—É –≤ —ñ—Å—Ç–æ—Ä—ñ—ó —ñ–Ω—Ñ–æ—Ä–º–∞—Ü—ñ–π–Ω–∏—Ö —Ç–µ—Ö–Ω–æ–ª–æ–≥—ñ–π.[5]

–í—Å–µ—Ä–µ–¥–∏–Ω—ñ —Å–∞–º–æ—ó IBM —Ç–æ–π —Ñ–∞–∫—Ç, —â–æ —ó—Ö –≤–∏–ø–µ—Ä–µ–¥–∏–ª–∞ –Ω–µ–≤–µ–ª–∏–∫–∞ Control Data Corporation, —Å–ø—Ä–∏–π–º–∞–≤—Å—è –¥–æ—Å–∏—Ç—å –≤–∞–∂–∫–æ.[6]

Керівника проєкту Стівена Данвелла (Stephen W. Dunwell),[7] було спочатку звинувачено у «провалі»,[8] але коли стало зрозуміло, що успіх наступника Stretch — лінійки System/360 — є безумовним — реабілітовано (керівництво IBM офіційно вибачилось перед Данвеллом, і навіть надало йому титул IBM Fellow у 1966-му році).[9]

–ù–µ–∑–≤–∞–∂–∞—é—á–∏ –Ω–∞ –Ω–µ–¥–æ—Å—Ç–∞—Ç–Ω—é —à–≤–∏–¥–∫–æ–¥—ñ—é, –±–∞–≥–∞—Ç–æ —ñ–¥–µ–π —ñ —Ç–µ—Ö–Ω–æ–ª–æ–≥—ñ–π Stretch –∑–Ω–∞–π—à–ª–∏ –ø–æ–¥–∞–ª—å—à–∏–π —Ä–æ–∑–≤–∏—Ç–æ–∫ —É –ª—ñ–Ω—ñ–π—Ü—ñ –º–∞—à–∏–Ω IBM System/360, —â–æ –¥–µ–±—é—Ç—É–≤–∞–ª–∞ 1964-–≥–æ —Ä–æ–∫—É.

–Ü—Å—Ç–æ—Ä—ñ—è —Ä–æ–∑—Ä–æ–±–∫–∏

–ù–∞ –ø–æ—á–∞—Ç–∫—É 1955 —Ä–æ–∫—É –¥–æ–∫—Ç–æ—Ä –ï–¥–≤–∞—Ä–¥ –¢–µ–ª–ª–µ—Ä –∑ –Ý–∞–¥—ñ–∞—Ü—ñ–π–Ω–æ—ó –õ–∞–±–æ—Ä–∞—Ç–æ—Ä—ñ—ó –ö–∞–ª—ñ—Ñ–æ—Ä–Ω—ñ–π—Å—å–∫–æ–≥–æ –£–Ω—ñ–≤–µ—Ä—Å–∏—Ç–µ—Ç—É —Ä–æ–∑–ø–æ—á–∞–≤ –ø–æ—à—É–∫ —Å–∏—Å—Ç–µ–º–∏ –¥–ª—è –Ω–∞—É–∫–æ–≤–∏—Ö –æ–±—á–∏—Å–ª–µ–Ω—å –≤ –≥–∞–ª—É–∑—ñ –≥—ñ–¥—Ä–æ–¥–∏–Ω–∞–º—ñ–∫–∏. –¢–µ–ª–ª–µ—Ä –∑–≤–µ—Ä–Ω—É–≤—Å—è –¥–æ IBM —Ç–∞ UNIVAC; —Å–∏—Å—Ç–µ–º–∞ –º–∞–ª–∞ –Ω–∞–∑–∏–≤–∞—Ç–∏—Å—å Livermore Automatic Reaction Calculator, –∞–±–æ LARC. –ö–∞—Ç–±–µ—Ä—Ç –ì–µ—Ä–¥ (Cuthbert Hurd), –≤–∏–∫–æ–Ω–∞–≤—á–∏–π –¥–∏—Ä–µ–∫—Ç–æ—Ä —É IBM, –æ—Ü—ñ–Ω–∏–≤ –≤–∞—Ä—Ç—ñ—Å—Ç—å —Ç–∞–∫–æ—ó —Å–∏—Å—Ç–µ–º–∏ –ø—Ä–∏–±–ª–∏–∑–Ω–æ —É 2,5 –º—ñ–ª—å–π–æ–Ω—ñ–≤ –¥–æ–ª–∞—Ä—ñ–≤, –∞ –ø—Ä–æ–¥—É–∫—Ç–∏–≤–Ω—ñ—Å—Ç—å ‚Äî 1..2 MIPS.[10]:12 –°–∏—Å—Ç–µ–º—É –º–∞–ª–æ –±—É—Ç–∏ –∑–¥–∞–Ω–æ –¥–æ –µ–∫—Å–ø–ª—É–∞—Ç–∞—Ü—ñ—ó —á–µ—Ä–µ–∑ ¬´–¥–≤–∞-—Ç—Ä–∏ —Ä–æ–∫–∏¬ª –ø—ñ—Å–ª—è –ø—ñ–¥–ø–∏—Å–∞–Ω–Ω—è –∫–æ–Ω—Ç—Ä–∞–∫—Ç—É.

–ù–∞ –∑–∞–≤–æ–¥—ñ IBM —É –ü–æ—É–∫—ñ–ø–∑—ñ –Ω–µ–≤–µ–ª–∏–∫–∞ –∫–æ–º–∞–Ω–¥–∞, –¥–æ —è–∫–æ—ó –≤—Ö–æ–¥–∏–ª–∏ –î–∂–æ–Ω “ê—Ä—ñ—Ñ—Ñ—ñ—Ç —ñ –î–∂–∏–Ω –ê–º–¥–∞–ª—å, –ø–æ—á–∞–ª–∞ —Ä–æ–±–æ—Ç—É –Ω–∞–¥ –¥–∏–∑–∞–π–Ω–æ–º. –£ –º–æ–º–µ–Ω—Ç –∫–æ–ª–∏ –≤–æ–Ω–∏ –∑–∞–∫—ñ–Ω—á–∏–ª–∏ —ñ –±—É–ª–∏ –≥–æ—Ç–æ–≤—ñ –ø—Ä–µ–¥—Å—Ç–∞–≤–∏—Ç–∏ –ø—Ä–æ–µ–∫—Ç, —ñ–Ω–∂–µ–Ω–µ—Ä –Ý–∞–ª—å—Ñ –ü–∞–ª–º–µ—Ä –∑—É–ø–∏–Ω–∏–≤ —ó—Ö –∑—ñ —Å–ª–æ–≤–∞–º–∏ ¬´—Ü–µ –ø–æ–º–∏–ª–∫–∞¬ª.[10]:12 –ó–∞–ø—Ä–æ–ø–æ–Ω–æ–≤–∞–Ω–∏–π –¥–∏–∑–∞–π–Ω –º–∞–≤ –±—É—Ç–∏ —Ä–µ–∞–ª—ñ–∑–æ–≤–∞–Ω–∏–π –∞–±–æ –Ω–∞ —Ç–æ—á–∫–æ–≤–∏—Ö, –∞–±–æ –Ω–∞ –ø–æ–≤–µ—Ä—Ö–Ω–µ–≤–æ-–±–∞—Ä'—î—Ä–Ω–∏—Ö —Ç—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä–∞—Ö ‚Äî –æ–±–∏–¥–≤–∞ —Ü—ñ —Ç–∏–ø–∏, —è–∫ –Ω–∞ —Ç–æ–π —á–∞—Å –≤–∂–µ —Å—Ç–∞–ª–æ –≤—ñ–¥–æ–º–æ, –ø–æ—Å—Ç—É–ø–∞–ª–∏—Å—è —É —à–≤–∏–¥–∫–æ–¥—ñ—ó —â–æ–π–Ω–æ –≤–∏–Ω–∞–π–¥–µ–Ω–∏–º –¥–∏—Ñ—É–∑—ñ–π–Ω–∏–º —Ç—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä–∞–º.[10]:12

IBM проінформувала Ліверморську лабораторію, що розриває контракт, але натомість запропонувала кардинально кращу систему: «Ми не будуватимемо ту машину для вас, ми хочемо збудувати щось набагато краще! Ми не знаємо точно, скільки зусиль і коштів це потребуватиме, але оцінюємо, що ще приблизно один мільйон доларів і один рік. Ми не знаємо точно, наскільки швидко вона працюватиме — десь 10 мільйонів інструкцій за секунду»."[10]:13 Втім, ці цифри не вразили Лівермор, і у травні 1955-го лабораторія оголосила, що UNIVAC виграв контракт на LARC, і що нове ім'я проекту — Livermore Automatic Research Computer. LARC було поставлено і здано до експлуатації у червні 1960-го року.[11]

У вересні 1955-го, на хвилі побоювань, що Лос-Аламоська національна лабораторія також замовить LARC, IBM презентувала чорновий варіант швидкодіючого двійкового комп'ютера на основі дизайну, який відхилили у Ліверморі. У Лос-Аламосі зацікавились, і у січні 1956-го проект Stretch було формально розпочато. У листопаді 1956-го IBM підписав контракт, з досить амбітними цілями щодо продуктивності системи на рівні «принаймні у 100 разів вищому, ніж у IBM 704» (тобто 4 MIPS). Здача проекта замовникові планувалася у 1960 році.

–ü—ñ–¥ —á–∞—Å –ø—Ä–æ–µ–∫—Ç—É–≤–∞–Ω–Ω—è —ñ –ø–æ—á–∞—Ç–∫–æ–≤–∏—Ö –≤–∏–ø—Ä–æ–±—É–≤–∞–Ω—å —Å—Ç–∞–ª–æ –∑—Ä–æ–∑—É–º—ñ–ª–æ, —â–æ —Ç–∞–∫—Ç–æ–≤—É —á–∞—Å—Ç–æ—Ç—É –ø—Ä–æ—Ü–µ—Å–æ—Ä–∞ –¥–æ–≤–µ–¥–µ—Ç—å—Å—è –∑–Ω–∏–∑–∏—Ç–∏, —ñ —â–æ –Ω–∞–π—ñ–º–æ–≤—ñ—Ä–Ω—ñ—à–µ Stretch –Ω–µ –¥–æ—Å—è–≥–Ω–µ –ø–æ—Å—Ç–∞–≤–ª–µ–Ω–∏—Ö —Ü—ñ–ª–µ–π –∑—ñ —à–≤–∏–¥–∫–æ–¥—ñ—ó. –í—Ç—ñ–º, –ø—Ä–æ–¥—É–∫—Ç–∏–≤–Ω—ñ—Å—Ç—å –º–∞–ª–∞ –≤–∏–π—Ç–∏ —è–∫ –º—ñ–Ω—ñ–º—É–º –Ω–∞ —Ä—ñ–≤–Ω—ñ 60-–∫—Ä–∞—Ç–Ω–æ—ó IBM 704. –£ 1960-–º—É –±—É–ª–æ –≤—Å—Ç–∞–Ω–æ–≤–ª–µ–Ω–æ —Ü—ñ–Ω—É, 13,5 –º—ñ–ª—å–π–æ–Ω–∞ –¥–æ–ª–∞—Ä—ñ–≤. –£ 1961-–º—É –∑–∞–ø—É—Å–∫ –ø—Ä–æ–≥—Ä–∞–º–∏ —Ç–µ—Å—Ç—É –ø—Ä–æ–¥—É–∫—Ç–∏–≤–Ω–æ—Å—Ç—ñ –ø–æ–∫–∞–∑–∞–≤, —â–æ —Ä–µ–∞–ª—å–Ω–∞ —à–≤–∏–¥–∫–æ–¥—ñ—è –±—É–¥–µ –ª–∏—à–µ –Ω–∞ —Ä—ñ–≤–Ω—ñ 30-–∫—Ä–∞—Ç–Ω–æ—ó IBM 704 (—Ç–æ–±—Ç–æ 1,2 MIPS). –¶–µ –≤–∏–∫–ª–∏–∫–∞–ª–æ —Ä–æ–∑–≥—É–±–ª–µ–Ω–Ω—è —ñ –∑–±–µ–Ω—Ç–µ–∂–µ–Ω–Ω—è —É IBM, —ñ, —è–∫ –Ω–∞—Å–ª—ñ–¥–æ–∫, —É —Ç—Ä–∞–≤–Ω—ñ 1961-–≥–æ –£–æ—Ç—Å–æ–Ω –∞–Ω–æ–Ω—Å—É–≤–∞–≤ –∑–Ω–∏–∂–µ–Ω–Ω—è —Ü—ñ–Ω–∏ –Ω–∞ –≤—Å—ñ –∑–∞–º–æ–≤–ª–µ–Ω—ñ IBM 7030 (–¥–æ 7,8 –º—ñ–ª—å–π–æ–Ω–∞ –¥–æ–ª–∞—Ä—ñ–≤), —ñ –ø—Ä–∏–ø–∏–Ω–µ–Ω–Ω—è –ø—Ä–æ–¥–∞–∂—É –º–∞—à–∏–Ω–∏ –Ω–æ–≤–∏–º –∑–∞–º–æ–≤–Ω–∏–∫–∞–º.

Додавання операндів з рухомою комою у IBM 7030 здійснювалося за 1,38..1,5 мікросекунд, множення — 2,48..2,70 мікросекунд, ділення — за 9..9,9 мікросекунд.

–í–ø–ª–∏–≤ –Ω–∞ —Ç–µ—Ö–Ω–æ–ª–æ–≥—ñ—é

Незважаючи на загальне сприйняття IBM 7030 як невдалої системи, багато технологічних рішень і ідей з цієї машини знайшли своє застосування в успішних комп'ютерах майбутнього. Транзисторні логічні схеми, побудовані зі стандартних блоків (Стандартна Модульна Система, SMS) стали основою лінійки машин IBM 7090 (наукові комп'ютери), IBM 7070 і 7080 (бізнес-комп'ютери), сімейств IBM 7040 і IBM 1400, а також невеликого наукового комп'ютера IBM 1620. Феритова пам'ять моделі 7302 Model I застосовувалася також у IBM 7090, IBM 7070 and IBM 7080. Багатозадачність, захист пам'яті, узагальнена схема переривань, восьмибітний байт для вводу-виводу[a] — всі ці інновації знайшли подальший розвиток у лінійці IBM System/360.

Стівен Данвелл, менеджер проекту, якого зробили «цапом-відбувайлом» за невдачі IBM 7030 на ринку, невдовзі після феноменально успішного початку продаж серії System/360 у 1964-му році відзначив, що більшість ключових компонентів серії було випробувано у машині Stretch.[12] 1966-го перед ним вибачились і надали титул IBM Fellow — висока відзнака, що дозволяє вести дослідження на власний вибір використовуючи ресурси компанії.[12]

Конвеєр команд, попередня вибірка і декодування інструкції, паралельні банки пам'яті — ці інновації знайшли своє застосування в пізніших проектах суперкомп'ютерів, таких як IBM System/360 моделі 91 і 95, IBM System/370 моделі 195, і серії IBM 3090, а також у комп'ютерах інших виробників. У більшості сучасних мікропроцесорів ці технології також активно використовуються.

–ö–æ–Ω—Å—Ç—Ä—É–∫—Ü—ñ—è –∞–ø–∞—Ä–∞—Ç—É—Ä–∏

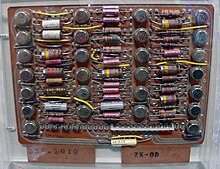

–î—Ä—É–∫–æ–≤–∞–Ω–∞ –ø–ª–∞—Ç–∞ –∑ IBM 7030, –≤ –º—É–∑–µ—ó Bradbury Science Museum, –õ–æ—Å-–ê–ª–∞–º–æ—Å.

–î—Ä—É–∫–æ–≤–∞–Ω–∞ –ø–ª–∞—Ç–∞ –∑ IBM 7030, –≤ –º—É–∑–µ—ó Bradbury Science Museum, –õ–æ—Å-–ê–ª–∞–º–æ—Å.

–ü—Ä–æ—Ü–µ—Å–æ—Ä IBM 7030 –ø–æ–±—É–¥–æ–≤–∞–Ω–∏–π –Ω–∞ –æ—Å–Ω–æ–≤—ñ —Å—Ö–µ–º –µ–º—ñ—Ç–µ—Ä–Ω–æ-–∑–≤'—è–∑–∞–Ω–æ—ó –ª–æ–≥—ñ–∫–∏.[13]

Всього було 18 типів «стандартних модульних плат» (SMS, Standard Modular System): 4025 двосторонніх (на ілюстрації) і 18747 односторонніх, на яких розміщувалося 169100 транзисторів. Машина споживала 21 кВт від мережі.[14]:54 Транзистори — германієві, дрейфові, підвищеної швидкодії (з робочою частотою до 100 МГц), як n-p-n, так і p-n-p структури, кожен споживав потужність приблизно 50 мВт.[14]:57 У деяких схемах використовувався «третій рівень напруги». Мінімальна затримка проходження логічного сигналу була на рівні 20 нс. У частинах схеми, що вимагали особливо високої швидкодії, застосовувалась логіка на емітерних повторювачах (це дозволяло знизити затримку ще на 10 нс).[14]:55

Тип феритової пам'яті — аналогічний машині IBM 7090.[14]:58

–Ü–Ω—Å—Ç–∞–ª—è—Ü—ñ—ó

- –õ–æ—Å-–ê–ª–∞–º–æ—Å—å–∫–∞ –Ω–∞—Ü—ñ–æ–Ω–∞–ª—å–Ω–∞ –ª–∞–±–æ—Ä–∞—Ç–æ—Ä—ñ—è, –ø–æ—Å—Ç–∞–≤–∫–∞: –∫–≤—ñ—Ç–µ–Ω—å 1961, –ø–æ—á–∞—Ç–æ–∫ —Ä–æ–±–æ—Ç–∏: —Ç—Ä–∞–≤–µ–Ω—å 1961, –∑—É–ø–∏–Ω–∫–∞ —Å–∏—Å—Ç–µ–º–∏: 21 —á–µ—Ä–≤–Ω—è 1971.

- –ê–≥–µ–Ω—Ç—Å—Ç–≤–æ –Ω–∞—Ü—ñ–æ–Ω–∞–ª—å–Ω–æ—ó –±–µ–∑–ø–µ–∫–∏ –°–ø–æ–ª—É—á–µ–Ω–∏—Ö –®—Ç–∞—Ç—ñ–≤: –∑ –ª—é—Ç–æ–≥–æ 1962 —Ä–æ–∫—É (–ø—Ä–æ—Ü–µ—Å–æ—Ä —Å–∏—Å—Ç–µ–º–∏ IBM 7950 Harvest) –ø–æ 1976 —Ä—ñ–∫ (—Å–∏—Å—Ç–µ–º–∞ –∞–≤—Ç–æ–º–∞—Ç–∏—á–Ω–æ—ó –ø–æ–¥–∞—á—ñ –∫–∞—Ä—Ç—Ä–∏–¥–∂—ñ–≤ –º–∞–≥–Ω—ñ—Ç–Ω–æ—ó —Å—Ç—Ä—ñ—á–∫–∏ IBM 7955 –ø–æ—á–∞–ª–∞ –¥–∞–≤–∞—Ç–∏ –∑–±–æ—ó —á–µ—Ä–µ–∑ –∑–Ω–æ—à–µ–Ω—ñ—Å—Ç—å –∫–æ–º–ø–æ–Ω–µ–Ω—Ç—ñ–≤, —Ç–æ–º—É –≤—Å—é —Å–∏—Å—Ç–µ–º—É HARVEST –±—É–ª–æ –≤–∏—Ä—ñ—à–µ–Ω–æ —Å–ø–∏—Å–∞—Ç–∏).

- –õ—ñ–≤–µ—Ä–º–æ—Ä—Å—å–∫–∞ –Ω–∞—Ü—ñ–æ–Ω–∞–ª—å–Ω–∞ –ª–∞–±–æ—Ä–∞—Ç–æ—Ä—ñ—è.

- –¶–µ–Ω—Ç—Ä –ê—Ç–æ–º–Ω–æ—ó –ó–±—Ä–æ—ó –ê–ª–¥–µ—Ä–º–∞—Å—Ç–æ–Ω, –ê–Ω–≥–ª—ñ—è.

- –ë—é—Ä–æ –ø–æ–≥–æ–¥–∏ –°–ø–æ–ª—É—á–µ–Ω–∏—Ö –®—Ç–∞—Ç—ñ–≤.

- –ö–æ—Ä–ø–æ—Ä–∞—Ü—ñ—è MITRE: –º–∞—à–∏–Ω–∞ –µ–∫—Å–ø–ª—É–∞—Ç—É–≤–∞–ª–∞—Å—è –¥–æ —Å–µ—Ä–ø–Ω—è 1971-–≥–æ; –Ω–∞–≤–µ—Å–Ω—ñ 1972-–≥–æ –ø—Ä–æ–¥–∞–Ω–∞ —É–Ω—ñ–≤–µ—Ä—Å–∏—Ç–µ—Ç—É –ë—Ä—ñ–≥–∞–º–∞ –Ø–Ω–≥–∞, –¥–µ –≤–∏–∫–æ—Ä–∏—Å—Ç–æ–≤—É–≤–∞–ª–∞—Å—è —É –¥–µ–ø–∞—Ä—Ç–∞–º–µ–Ω—Ç—ñ —Ñ—ñ–∑–∏–∫–∏ –∞–∂ –¥–æ –∑—É–ø–∏–Ω–∫–∏ —ñ —Ä–æ–∑–±–∏—Ä–∞–Ω–Ω—è —É 1982-–º—É.

- Військово-морські сили США, центр у Далґрені, Вірджинія.

- IBM.

- –ö–æ–º—ñ—Å–∞—Ä—ñ–∞—Ç –∞—Ç–æ–º–Ω–æ—ó –µ–Ω–µ—Ä–≥–µ—Ç–∏–∫–∏ –§—Ä–∞–Ω—Ü—ñ—ó.

IBM 7030 –∑ –ª–∞–±–æ—Ä–∞—Ç–æ—Ä—ñ—ó –õ–æ—É—Ä–µ–Ω—Å–∞ –õ—ñ–≤–µ—Ä–º–æ—Ä–∞ (–æ–∫—Ä—ñ–º —Ñ–µ—Ä–∏—Ç–æ–≤–æ—ó –ø–∞–º'—è—Ç—ñ) —ñ —á–∞—Å—Ç–∏–Ω–∏ –º–∞—à–∏–Ω–∏, —â–æ –ø—Ä–∞—Ü—é–≤–∞–ª–∞ —É MITRE Corporation / –£–Ω—ñ–≤–µ—Ä—Å–∏—Ç–µ—Ç—ñ –ë—Ä—ñ–≥–∞–º–∞ –Ø–Ω–≥–∞, –∑–∞—Ä–∞–∑ –∑–Ω–∞—Ö–æ–¥—è—Ç—å—Å—è —É –∫–æ–ª–µ–∫—Ü—ñ—ó –ú—É–∑–µ—é –∫–æ–º–ø'—é—Ç–µ—Ä–Ω–æ—ó —ñ—Å—Ç–æ—Ä—ñ—ó —É –ú–∞—É–Ω—Ç—ñ–Ω-–í'—é, –ö–∞–ª—ñ—Ñ–æ—Ä–Ω—ñ—è.

–ê—Ä—Ö—ñ—Ç–µ–∫—Ç—É—Ä–∞

–§–æ—Ä–º–∞—Ç–∏ –¥–∞–Ω–∏—Ö

- Числа з рухомою комою — змінної ширини, зберігаються або у двійковій (від 1 до 64 біт), або у десятковій (від 1 до 16 цифр) формі, без знаку або зі знаком. При використанні десяткової форми цифри — змінної розрядності (від 4 до 8 біт).

- Числа з рухомою комою мають 1 біт «прапорця експоненти», 10 біт власне експоненти, 1 біт знаку експоненти, 48 біт величини, і 4-бітний знак (у форматі знак/величина).

- Алфавітно-цифрові символи — змінної розрядності (8 біт або менше).

- –ó–º—ñ–Ω–Ω–∞ —à–∏—Ä–∏–Ω–∞ –±–∞–π—Ç–∞ (–≤—ñ–¥ 1 –¥–æ 8 –±—ñ—Ç).[15]

–§–æ—Ä–º–∞—Ç —ñ–Ω—Å—Ç—Ä—É–∫—Ü—ñ–π

Ширина інструкції — 32 або 64 біти.

–Ý–µ–≥—ñ—Å—Ç—Ä–∏

–Ý–µ–≥—ñ—Å—Ç—Ä–∏ –≤—ñ–¥–æ–±—Ä–∞–∂–∞—é—Ç—å—Å—è –Ω–∞ –ø–µ—Ä—à—ñ 32 –∞–¥—Ä–µ—Å–∏ –ø–∞–º'—è—Ç—ñ.[16]

| –ê–¥—Ä–µ—Å–∞ |

–ú–Ω–µ–º–æ–Ω—ñ–∫–∞ |

–Ý–µ–≥—ñ—Å—Ç—Ä |

–Ý–æ–∑—Ç–∞—à—É–≤–∞–Ω–Ω—è

|

| 0 |

$Z |

64-—Ä–æ–∑—Ä—è–¥–Ω–∏–π –Ω—É–ª—å: —Ç—ñ–ª—å–∫–∏ –¥–ª—è —á–∏—Ç–∞–Ω–Ω—è (–∑–∞–≤–∂–¥–∏ —á–∏—Ç–∞—î—Ç—å—Å—è –Ω—É–ª—å)

|

–ì–æ–ª–æ–≤–Ω–∞ –ø–∞–º'—è—Ç—å

|

| 1

|

$IT |

інтервальний таймер (розряди 0..18): значення зменшується з частотою 1024 Гц, переповнення кожні 8,5 хвилини, при нульовому значенні виставляє «time signal indicator» у індикаторному регістрі

|

–Ü–Ω–¥–µ–∫—Å–Ω–∞ –ø–∞–º'—è—Ç—å

|

| $TC |

36-—Ä–æ–∑—Ä—è–¥–Ω–∏–π —Ç–∞–π–º–µ—Ä (—Ä–æ–∑—Ä—è–¥–∏ 28..63): –ø—ñ–¥—Ä–∞—Ö–æ–≤—É—î –∫—ñ–ª—å–∫—ñ—Å—Ç—å —Ü–∏–∫–ª—ñ–≤ –ø–æ 1024 –ì—Ü, –±—ñ—Ç–∏ 38..63 –∑–±—ñ–ª—å—à—É—é—Ç—å—Å—è —Ä–∞–∑ –Ω–∞ —Å–µ–∫—É–Ω–¥—É, –ø–µ—Ä–µ–ø–æ–≤–Ω–µ–Ω–Ω—è –ø—Ä–∏–±–ª–∏–∑–Ω–æ –∑–∞ 777 –¥—ñ–±.

|

| 2

|

$IA |

18-—Ä–æ–∑—Ä—è–¥–Ω–∞ –∞–¥—Ä–µ—Å–∞ –ø–µ—Ä–µ—Ä–∏–≤–∞–Ω–Ω—è

|

–ì–æ–ª–æ–≤–Ω–∞ –ø–∞–º'—è—Ç—å

|

| 3

|

$UB |

18-—Ä–æ–∑—Ä—è–¥–Ω–∞ –∞–¥—Ä–µ—Å–∞ –≤–µ—Ä—Ö–Ω—å–æ—ó –≥—Ä–∞–Ω–∏—Ü—ñ (upper boundary address, –±—ñ—Ç–∏ 0-17)

|

–¢—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä–Ω–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä

|

| $LB |

18-—Ä–æ–∑—Ä—è–¥–Ω–∞ –∞–¥—Ä–µ—Å–∞ –Ω–∏–∂–Ω—å–æ—ó –≥—Ä–∞–Ω–∏—Ü—ñ (lower boundary address, –±—ñ—Ç–∏ 32-49)

|

|

1-—Ä–æ–∑—Ä—è–¥–Ω–∏–π –∫–æ–Ω—Ç—Ä–æ–ª—å –≥—Ä–∞–Ω–∏—Ü—ñ (–±—ñ—Ç 57): –≤–∏–∑–Ω–∞—á–∞—î –∑–∞—Ö–∏—â–µ–Ω—ñ—Å—Ç—å/–Ω–µ–∑–∞—Ö–∏—â–µ–Ω—ñ—Å—Ç—å –∞–¥—Ä–µ—Å–∏ –≤ –º–µ–∂–∞—Ö –≥—Ä–∞–Ω–∏—Ü—ñ

|

| 4

|

|

64-—Ä–æ–∑—Ä—è–¥–Ω–∏–π —Å–ª—É–∂–±–æ–≤–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä

|

–ì–æ–ª–æ–≤–Ω–∞ –ø–∞–º'—è—Ç—å

|

| 5

|

$CA |

–∞–¥—Ä–µ—Å–∞ –∫–∞–Ω–∞–ª—É (—Ä–æ–∑—Ä—è–¥–∏ 12..18): —Ç—ñ–ª—å–∫–∏ –¥–ª—è —á–∏—Ç–∞–Ω–Ω—è, –≤—Å—Ç–∞–Ω–æ–≤–ª—é—î—Ç—å—Å—è –ø—Ä–æ—Ü–µ—Å–æ—Ä–æ–º –≤–≤–æ–¥—É-–≤–∏–≤–æ–¥—É

|

–¢—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä–Ω–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä

|

| 6

|

$CPUS |

–±—ñ—Ç–∏ —ñ–Ω—à–∏—Ö –ø—Ä–æ—Ü–µ—Å–æ—Ä—ñ–≤ (0..18): –º–µ—Ö–∞–Ω—ñ–∑–º –ø–æ–≤—ñ–¥–æ–º–ª–µ–Ω—å –¥–ª—è –∫–ª–∞—Å—Ç–µ—Ä–∞ –¥–æ 20 –¶–ü

|

–¢—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä–Ω–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä

|

| 7

|

$LZC |

–ª—ñ—á–∏–ª—å–Ω–∏–∫ –ª—ñ–≤–∏—Ö –Ω—É–ª—å–æ–≤–∏—Ö —Ä–æ–∑—Ä—è–¥—ñ–≤ (–±—ñ—Ç–∏ 17..23): –∫—ñ–ª—å–∫—ñ—Å—Ç—å –ø–æ—á–∞—Ç–∫–æ–≤–∏—Ö –Ω—É–ª—å–æ–≤–∏—Ö –±—ñ—Ç —Ä–µ–∑—É–ª—å—Ç–∞—Ç—É –æ–ø–µ—Ä–∞—Ü—ñ—ó

|

–¢—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä–Ω–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä

|

| $AOC |

–ª—ñ—á–∏–ª—å–Ω–∏–∫ –æ–¥–∏–Ω–∏—á–Ω–∏—Ö —Ä–æ–∑—Ä—è–¥—ñ–≤ (–±—ñ—Ç–∏ 44..50): –∫—ñ–ª—å–∫—ñ—Å—Ç—å –æ–¥–∏–Ω–∏—á–Ω–∏—Ö –±—ñ—Ç —Ä–µ–∑—É–ª—å—Ç–∞—Ç—É –æ–ø–µ—Ä–∞—Ü—ñ—ó

|

| 8

|

$L |

–õ—ñ–≤–∞ –ø–æ–ª–æ–≤–∏–Ω–∞ 128-—Ä–æ–∑—Ä—è–¥–Ω–æ–≥–æ –∞–∫—É–º—É–ª—è—Ç–æ—Ä–∞

|

–¢—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä–Ω–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä

|

| 9

|

$R |

–ü—Ä–∞–≤–∞ –ø–æ–ª–æ–≤–∏–Ω–∞ 128-—Ä–æ–∑—Ä—è–¥–Ω–æ–≥–æ –∞–∫—É–º—É–ª—è—Ç–æ—Ä–∞

|

| 10

|

$SB |

–±–∞–π—Ç –∑–Ω–∞–∫—É –∞–∫—É–º—É–ª—è—Ç–æ—Ä–∞ (–±—ñ—Ç–∏ 0..7)

|

| 11

|

$IND |

—Ä–µ–≥—ñ—Å—Ç—Ä —ñ–Ω–¥–∏–∫–∞—Ç–æ—Ä–∞ (–±—ñ—Ç–∏ 0..19)

|

–¢—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä–Ω–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä

|

| 12

|

$MASK |

64-—Ä–æ–∑—Ä—è–¥–Ω–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä –º–∞—Å–∫–∏r: –±—ñ—Ç–∏ 0..19 –∑–∞–≤–∂–¥–∏ 1, –±—ñ—Ç–∏ 20..47 –∑ –º–æ–∂–ª–∏–≤—ñ—Å—Ç—é –∑–∞–ø–∏—Å—É, –±—ñ—Ç–∏ 48..63 –∑–∞–≤–∂–¥–∏ 0

|

–¢—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä–Ω–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä

|

| 13

|

$RM |

64-—Ä–æ–∑—Ä—è–¥–Ω–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä –∑–∞–ª–∏—à–∫—É: –≤—Å—Ç–∞–Ω–æ–≤–ª—é—î—Ç—å—Å—è —ñ–Ω—Å—Ç—Ä—É–∫—Ü—ñ—è–º–∏ –¥—ñ–ª–µ–Ω–Ω—è (—Ü—ñ–ª–æ–≥–æ —ñ –∑ —Ä—É—Ö–æ–º–æ—é –∫–æ–º–æ—é)

|

–ì–æ–ª–æ–≤–Ω–∞ –ø–∞–º'—è—Ç—å

|

| 14

|

$FT |

64-розрядний регістр дільника (може бути змінений лише інструкцією «load factor»)

|

–ì–æ–ª–æ–≤–Ω–∞ –ø–∞–º'—è—Ç—å

|

| 15

|

$TR |

64-—Ä–æ–∑—Ä—è–¥–Ω–∏–π —Ç—Ä–∞–Ω–∑–∏—Ç–Ω–∏–π —Ä–µ–≥—ñ—Å—Ç—Ä

|

–ì–æ–ª–æ–≤–Ω–∞ –ø–∞–º'—è—Ç—å

|

16

…

31

|

$X0

…

$X15 |

64-—Ä–æ–∑—Ä—è–¥–Ω—ñ —ñ–Ω–¥–µ–∫—Å–Ω—ñ —Ä–µ–≥—ñ—Å—Ç—Ä–∏ (–≤—Å—å–æ–≥–æ 16)

|

–Ü–Ω–¥–µ–∫—Å–Ω–∞ –ø–∞–º'—è—Ç—å

|

–ü–∞–º'—è—Ç—å

Об'єм феритової пам'яті — від 16K to 256K 64-розрядних слів, банками по 16K.

–ú–æ–¥—É–ª—ñ –ø–∞–º'—è—Ç—ñ –±—É–ª–æ –∑–∞–Ω—É—Ä–µ–Ω–æ –≤ –º–∞—Å—Ç–∏–ª–æ, –¥–ª—è —Å—Ç–∞–±—ñ–ª—ñ–∑–∞—Ü—ñ—ó –æ–ø–µ—Ä–∞—Ü—ñ–π–Ω–∏—Ö —Ö–∞—Ä–∞–∫—Ç–µ—Ä–∏—Å—Ç–∏–∫ —ñ —É–Ω–∏–∫–Ω–µ–Ω–Ω—è –ø–µ—Ä–µ–ø–∞–¥—É —Ç–µ–º–ø–µ—Ä–∞—Ç—É—Ä.

–ü—Ä–æ–≥—Ä–∞–º–æ–≤–µ –∑–∞–±–µ–∑–ø–µ—á–µ–Ω–Ω—è

–î–∏–≤. —Ç–∞–∫–æ–∂

- IBM 608, –ø–µ—Ä—à–∏–π –æ–±—á–∏—Å–ª—é–≤–∞–ª—å–Ω–∏–π –ø—Ä–∏—Å—Ç—Ä—ñ–π –Ω–∞ —Ç—Ä–∞–Ω–∑–∏—Å—Ç–æ—Ä–∞—Ö (–∫–∞–ª—å–∫—É–ª—è—Ç–æ—Ä –∑ –º–æ–∂–ª–∏–≤—ñ—Å—Ç—é –ø–µ—Ä–µ–∫–æ–º—É—Ç–∞—Ü—ñ—ó —Å—Ö–µ–º), –¥–æ—Å—Ç—É–ø–Ω–∏–π –Ω–∞ —Ä–∏–Ω–∫—É

–ü—Ä–∏–º—ñ—Ç–∫–∏

- ↑ Хоча у Stretch інструкції могли працювати з байтами довільної ширини, жоден наступний процесор від IBM таку схему не реалізовував. Однак, деякі машини від Burroughs, Control Data Corporation, DEC, General Electric, RCA, UNIVAC та інші мали підтримку байта змінної ширини — аж до ширини машинного слова

–î–∂–µ—Ä–µ–ª–∞

- ↑ «CDC 6600, спроектована Сеймуром Креєм, була майже втричі швидша за IBM 7030.» Making a World of Difference: Engineering Ideas into Reality. National Academy of Engineering. 2014. ISBN 0309312655.

- ↑ «У 1964 році CDC 6600 Крея витіснила Stretch з вершини найшвидших ЕОМ світу.» Andreas Sofroniou (2013). EXPERT SYSTEMS, KNOWLEDGE ENGINEERING FOR HUMAN REPLICATION. ISBN 1291595090.

- ‚Üë Some Early UK FORTRAN Compilers. –ê—Ä—Ö—ñ–≤ –æ—Ä–∏–≥—ñ–Ω–∞–ª—É –∑–∞ 27 —á–µ—Ä–≤–Ω—è 2017. –ü—Ä–æ—Ü–∏—Ç–æ–≤–∞–Ω–æ 26 –≥—Ä—É–¥–Ω—è 2017.

- ‚Üë HARTRAN Overview. –ê—Ä—Ö—ñ–≤ –æ—Ä–∏–≥—ñ–Ω–∞–ª—É –∑–∞ 15 –∂–æ–≤—Ç–Ω—è 2017. –ü—Ä–æ—Ü–∏—Ç–æ–≤–∞–Ω–æ 26 –≥—Ä—É–¥–Ω—è 2017.

- ‚Üë Widman, Jake (9 –∂–æ–≤—Ç–Ω—è 2008). Lessons Learned: IT's Biggest Project Failures. PCWorld. –ê—Ä—Ö—ñ–≤ –æ—Ä–∏–≥—ñ–Ω–∞–ª—É –∑–∞ 5 –ª–∏—Å—Ç–æ–ø–∞–¥–∞ 2012. –ü—Ä–æ—Ü–∏—Ç–æ–≤–∞–Ω–æ 23 –∂–æ–≤—Ç–Ω—è 2012.

- ↑ Відома цитата президента Т. Дж. Уотсона молодшого, де він запитує «Чому нас обійшла фірма, де працює 34 людини з прибиральником включно?»Watson Jr. memo about CDC 6600. 28 серпня 1963. Архів оригіналу за 3 січня 2018. Процитовано 26 грудня 2017.

- ‚Üë IBM Archives: Stephen W. Dunwell. IBM. –ê—Ä—Ö—ñ–≤ –æ—Ä–∏–≥—ñ–Ω–∞–ª—É –∑–∞ 15 —Ç—Ä–∞–≤–Ω—è 2017. –ü—Ä–æ—Ü–∏—Ç–æ–≤–∞–Ω–æ 26 –≥—Ä—É–¥–Ω—è 2017.

- ↑ «Stretch was considered a commercial failure, and Dunwell was sent into …» Smotherman, Mark; Spicer, Dag. IBM's Single-Processor Supercomputer Efforts.

- ↑ « to pursue any research he wished.» Wolfgang Saxon (24 березня 1994). S. W. Dunwell, 80, Engineer at I.B.M.; Designed Computers. The New York Times. Архів оригіналу за 15 жовтня 2017. Процитовано 26 грудня 2017.

- ↑ а б в г Bob Evans (Summer 1984). IBM System/360. The Computer Museum Report. с. 8—18.

- ‚Üë Charles Cole. The Remington Rand Univac LARC. –ê—Ä—Ö—ñ–≤ –æ—Ä–∏–≥—ñ–Ω–∞–ª—É –∑–∞ 26 –∂–æ–≤—Ç–Ω—è 2018. –ü—Ä–æ—Ü–∏—Ç–æ–≤–∞–Ω–æ 26 –≥—Ä—É–¥–Ω—è 2017.

- ‚Üë –∞ –± Simmons, William W.; Elsberry, Richard B. (1988), Inside IBM: the Watson years (a personal memoir), Pennsylvania, USA: Dorrance, —Å. 160, ISBN 978-0805931167, –∞—Ä—Ö—ñ–≤ –æ—Ä–∏–≥—ñ–Ω–∞–ª—É –∑–∞ 18 —á–µ—Ä–≤–Ω—è 2013, –ø—Ä–æ—Ü–∏—Ç–æ–≤–∞–Ω–æ 26 –≥—Ä—É–¥–Ω—è 2017. The memoir of a senior IBM executive, giving his recollections of his and IBM's experience from World War II into the 1970s..

- ↑ Rymaszewski, E. J. та ін. (1981). Semiconductor Logic Technology in IBM. IBM Journal of Research and Development. 25 (5): 607—608. doi:10.1147/rd.255.0603. ISSN 0018-8646. Архів оригіналу за 11 липня 2017. Процитовано 9 листопада 2017.

- ‚Üë –∞ –± –≤ –≥ Erich Bloch (1959). The Engineering Design of the Stretch Computer (PDF). Eastern Joint Computer Conference. –ê—Ä—Ö—ñ–≤ –æ—Ä–∏–≥—ñ–Ω–∞–ª—É (PDF) –∑–∞ 26 –≤–µ—Ä–µ—Å–Ω—è 2019. –ü—Ä–æ—Ü–∏—Ç–æ–≤–∞–Ω–æ 17 —Ç—Ä–∞–≤–Ω—è 2019.

- ↑ Mark Smotherman (July 2010). IBM Stretch (7030) — Aggressive Uniprocessor Parallelism. clemson.edu. Архів оригіналу за 2 жовтня 2017. Процитовано 7 грудня 2013.

- ‚Üë IBM 7030 Data Processing System Reference Manual (PDF). bitsavers.org. IBM. 1961. —Å. 34..38. –ê—Ä—Ö—ñ–≤ –æ—Ä–∏–≥—ñ–Ω–∞–ª—É (PDF) –∑–∞ 29 –≤–µ—Ä–µ—Å–Ω—è 2018. –ü—Ä–æ—Ü–∏—Ç–æ–≤–∞–Ω–æ 5 —Ç—Ä–∞–≤–Ω—è 2015.

- ‚Üë Roger B. Lazarus (1978). Computing at LASL in the 1940s and 1950s. –î–µ–ø–∞—Ä—Ç–∞–º–µ–Ω—Ç –µ–Ω–µ—Ä–≥–µ—Ç–∏–∫–∏ –°–®–ê. –ê—Ä—Ö—ñ–≤ –æ—Ä–∏–≥—ñ–Ω–∞–ª—É –∑–∞ 27 –≥—Ä—É–¥–Ω—è 2017. –ü—Ä–æ—Ü–∏—Ç–æ–≤–∞–Ω–æ 26 –≥—Ä—É–¥–Ω—è 2017.

- ‚Üë The IBM 7030 FORTRAN System (PDF). Computer History Museum. IBM Stretch Collection: International Business Machines Corporation. 1961. —Å. 36. –ê—Ä—Ö—ñ–≤ –æ—Ä–∏–≥—ñ–Ω–∞–ª—É (PDF) –∑–∞ 2 –∫–≤—ñ—Ç–Ω—è 2015. –ü—Ä–æ—Ü–∏—Ç–æ–≤–∞–Ω–æ 28 –ª—é—Ç–æ–≥–æ 2015.

–ü–æ—Å–∏–ª–∞–Ω–Ω—è