JTAG

|

Read other articles:

Artikel ini sebatang kara, artinya tidak ada artikel lain yang memiliki pranala balik ke halaman ini.Bantulah menambah pranala ke artikel ini dari artikel yang berhubungan atau coba peralatan pencari pranala.Tag ini diberikan pada Oktober 2022. Kejahatan sempurna adalah kejahatan yang tak terdeteksi, tidak dikaitkan dengan pelaku yang dapat diidentifikasi, tidak terpecahkan, atau tidak dapat diungkapkan dan menjadi semacam pencapaian teknis bagi si pelaku. Istilah ini digunakan sehari-hari da...

Pengatur waktu pada jam ini menggunakan aritmetika modulo 12. Dalam matematika dan khususnya pada teori bilangan aljabar, aritmetika modular adalah metode aritmetika untuk menyelesaikan permasalahan mengenai bilangan bulat. Ide dasar dari aritmetika modular adalah bekerja dengan sisa hasil pembagian bilangan, bukan dengan bilangan itu sendiri. Salah satu contoh dari aritmetika modular ada pada sistem 12-jam, di mana hari dibagi menjadi dua periode 12-jam. Jika sekarang jarum jam menunjukan pu...

لمعانٍ أخرى، طالع ميغيل أنخيل (توضيح). ميغيل أنخيل دياز معلومات شخصية الميلاد 27 يناير 1957 (67 سنة) تشالاتنانغو [لغات أخرى] الطول 1.79 م (5 قدم 10 1⁄2 بوصة) مركز اللعب مُدَافِع الجنسية السلفادور المسيرة الاحترافية1 سنوات فريق م. (هـ.) A.D. Chal...

Artikel ini tidak memiliki referensi atau sumber tepercaya sehingga isinya tidak bisa dipastikan. Tolong bantu perbaiki artikel ini dengan menambahkan referensi yang layak. Tulisan tanpa sumber dapat dipertanyakan dan dihapus sewaktu-waktu.Cari sumber: Daftar perguruan tinggi di Semarang – berita · surat kabar · buku · cendekiawan · JSTOR Berikut ini adalah Daftar Perguruan Tinggi atau Kampus di Kota Semarang Perguruan Tinggi Kedinasan Akademi Kepolisi...

Pulau NatalTerritory of Christmas Island (Inggris) Bendera Lambang Semboyan: —Lagu kebangsaan: Advance Australia Fair (Indonesia: Majulah Australia Jaya) Ibu kota(dan pemukiman terbesar)Flying Fish CoveBahasa resmiInggris • MelayuPemerintahanMonarki konstitusional• Raja Charles III• Gubernur Jenderal Peter Cosgrove• Administrator Natasha Griggs• Presiden Shire Gordon Thomson LegislatifShire CouncilTeritori eksternal Australia• Dikuasai oleh Im...

National university in Nagoya, Japan Not to be confused with Nagoya City University. Nagoya University名古屋大学Motto勇気ある知識人 (courageous intellectual)TypePublic (national)Established1871; 153 years ago (1871)(Chartered 1939)PresidentNaoshi SugiyamaAcademic staff3,847 (2020)Undergraduates9,585 (2020)Postgraduates6,187 (2020)LocationNagoya, Aichi, Japan35°09′17″N 136°58′01″E / 35.15472°N 136.96694°E / 35.15472; 136.96694Ca...

Bandar Udara SilampariSilampari AirportIATA: LLJICAO: WIPBInformasiJenisSipilMelayaniLubuklinggau, Sumatera SelatanLokasiLubuklinggau, Sumatera SelatanKetinggian dpl125 mdplKoordinat03°16′48″S 102°55′02″E / 3.28000°S 102.91722°E / -3.28000; 102.91722Koordinat: 03°16′48″S 102°55′02″E / 3.28000°S 102.91722°E / -3.28000; 102.91722Situs webllg.informasibandara.orgPetaBandar Udara SilampariLokasi di IndonesiaLandasan...

2013 single by Eros Ramazzotti featuring Nicole ScherzingerFino all'estasiCover for the Daddy's Groove RemixSingle by Eros Ramazzotti featuring Nicole Scherzingerfrom the album Noi ReleasedMay 24, 2013 (2013-05-24)Genre Pop Latin pop Length3:45LabelUniversalSongwriter(s) Eros Ramazzotti Luca Chiaravalli Anthony Preston Carlo Rizoli Saverio Grandi Producer(s) Ramazzotti Chiaravalli Preston Eros Ramazzotti singles chronology Un Angelo Disteso al Sole (2013) Fino all'esta...

穆罕默德·达乌德汗سردار محمد داود خان 阿富汗共和國第1任總統任期1973年7月17日—1978年4月28日前任穆罕默德·查希爾·沙阿(阿富汗國王)继任穆罕默德·塔拉基(阿富汗民主共和國革命委員會主席團主席) 阿富汗王國首相任期1953年9月7日—1963年3月10日君主穆罕默德·查希爾·沙阿 个人资料出生(1909-07-18)1909年7月18日 阿富汗王國喀布尔逝世1978年4月28日(...

بطولة العالم لكرة اليد للرجال 2007تفاصيل المسابقةالبلد المضيف ألمانياالتواريخ19 يناير – 4 فبرايرالفرق24الأماكن12 (في 12 مدينة مضيفة)المراكز النهائيةالبطل ألمانياالوصيف بولنداالمركز الثالث الدنماركالمركز الرابع فرنساإحصائيات المسابقةالمباريات الملعوبة9...

Swedish consumer cooperative This article needs additional citations for verification. Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed.Find sources: Kooperativa Förbundet – news · newspapers · books · scholar · JSTOR (October 2015) (Learn how and when to remove this message) Kooperativa FörbundetCompany typeCooperative FederationIndustryRetailFounded1899 (1899)Headquarter...

Public secondary school in Oswego, Kansas, United StatesOswego Junior Senior High SchoolAddress1501 Tomahawk TrailOswego, Kansas 67356United StatesCoordinates37°10′26″N 95°7′3″W / 37.17389°N 95.11750°W / 37.17389; -95.11750InformationSchool typepublic secondarySchool districtOswego USD 504SuperintendentDoug BeiselPrincipalRob SchneebergerTeaching staff20Grades7–12GendercoedEnrollment148 (2016-17)[1]Campus typeCommuter Town/RuralColor(s) Red&...

هذه المقالة تحتاج للمزيد من الوصلات للمقالات الأخرى للمساعدة في ترابط مقالات الموسوعة. فضلًا ساعد في تحسين هذه المقالة بإضافة وصلات إلى المقالات المتعلقة بها الموجودة في النص الحالي. (ديسمبر 2023) رحلة للسعادة تعديل مصدري - تعديل رحلة للسعادة هو عنوان برنامج تلفزيوني للد...

Chronologie de la Belgique ◄◄ 1939 1940 1941 1942 1943 1944 1945 1946 1947 ►► Chronologies Accueil par les Jeunesses hitlériennes flamandes d'une délégation de la Hitlerjugend allemande, à Bruxelles, le 2 mai 1943.Données clés 1940 1941 1942 1943 1944 1945 1946Décennies :1910 1920 1930 1940 1950 1960 1970Siècles :XVIIIe XIXe XXe XXIe XXIIeMillénaires :-Ier Ier IIe IIIe Chronologies géographiques Afrique Afrique ...

This article includes a list of references, related reading, or external links, but its sources remain unclear because it lacks inline citations. Please help improve this article by introducing more precise citations. (August 2016) (Learn how and when to remove this message) Be 4/6 12302Be 4/6 number 12302 in the 1930sType and originPower typeElectricBuilderBrown, Boveri & Cie (BBC)Build date1919Total produced1SpecificationsConfiguration: • UIC(1’B)(B1’)Gauge1,435&...

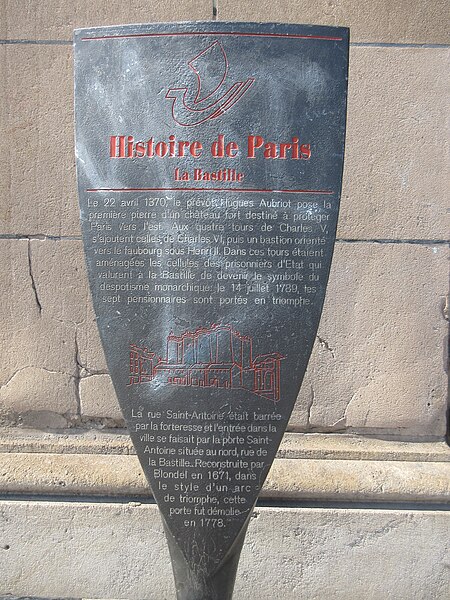

Pour les articles homonymes, voir Bastille. 4e, 11e, 12e arrtsPlace de la Bastille Place de la Bastille vue depuis les marches de l'Opéra ; à droite la colonne de Juillet. Situation Arrondissements 4e11e12e Quartiers ArsenalRoquetteQuinze-Vingts Voies desservies Rue du Faubourg-Saint-Antoine rue de la Roquetteboulevard de la Bastillerue de Lyonboulevard Henri-IVrue Saint-Antoineboulevard Beaumarchaisboulevard Richard-Lenoir Morphologie Longueur 215 m Largeur 150 m Histo...

Francia ai Giochi della XV OlimpiadeHelsinki 1952 Codice CIOFRA Comitato nazionaleComité National Olympique et Sportif Français Atleti partecipanti245 in 18 discipline Di cui uomini/donne214 - 31 PortabandieraIgnace Heinrich Medagliere Posizione 7ª 6 6 6 18 Cronologia olimpica (sommario)Giochi olimpici estivi 1896 · 1900 · 1904 · 1908 · 1912 · 1920 · 1924 · 1928 · 1932 · 1936 · 1948 · 1952 · 1956 ·...

Spanish colonial, and early post-colonial, administrative council that governed a municipality For a discussion of the contemporary Spanish and Latin American cabildo, see Ayuntamiento. 1810 meeting of the cabildo in Buenos Aires Depiction of the main cabildo buildings of the Viceroyalty of the Río de la Plata. A cabildo (Spanish pronunciation: [kaˈβildo]) or ayuntamiento (Spanish: [aʝuntaˈmjento]) was a Spanish colonial and early postcolonial administrative council that ...

Canadian ice hockey player (1915–1990) This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these messages) This article relies largely or entirely on a single source. Relevant discussion may be found on the talk page. Please help improve this article by introducing citations to additional sources.Find sources: Harvey Teno – news · newspapers · books · scholar · JSTOR (August...

Questa voce sull'argomento calciatori spagnoli è solo un abbozzo. Contribuisci a migliorarla secondo le convenzioni di Wikipedia. Segui i suggerimenti del progetto di riferimento. Jesús GarcíaNazionalità Spagna Altezza190 cm Peso78 kg Calcio RuoloDifensore Termine carriera2019 CarrieraGiovanili 1999-200? CP San Cristobal200?-2004 Terrassa2004-2009 Espanyol2010-2011 Juventus Squadre di club1 2009 Sabadell1 (0)2009-2010 Terrassa13 (0)2011-2012 Cuneo2...